# CMS32M67xx User Manual

Ultra-low power 32-bit microcontrollers based on ARM® Cortex®-M0+V1.0.1

#### Please note the following CMS IP policy

<sup>\*</sup> China Micro Semicon Co., Ltd. (hereinafter referred to as the Company) has applied for patents and holds absolute legal rights and interests. The patent rights associated with the Company's MCUs or other products have not been authorized for use, and any company, organization, or individual who infringes the Company's patent rights through improper means will be subject to all possible legal actions taken by the Company to curb the infringement and to recover any damages suffered by the Company as a result of the infringement or any illegal benefits obtained by the infringer.

$<sup>\</sup>star$  The name and logo of Cmsemicon are registered trademarks of the Company.

<sup>\*</sup> The Company reserves the right to further explain the reliability, functionality and design improvements of the products in the data sheet. However, the Company is not responsible for the use of the Specification Contents. The applications mentioned herein are for illustrative purposes only and the Company does not warrant and does not represent that these applications can be applied without further modification, nor does it recommend that its products be used in places that may cause harm to persons due to malfunction or other reasons. The Company's products are not authorized for use as critical components in lifesaving, life-sustaining devices or systems. The Company reserves the right to modify the products without prior notice. For the latest information, please visit the official website at www.mcu.com.cn.

#### **Documentation Instructions**

This manual is the technical reference manual for the CMS32M67xx controller product. The technical reference manual provides application notes on how to use this series of products. It contains detailed information on the structure, functional descriptions, operating modes, and register configurations of each functional module, with a dedicated chapter for each functional module.

The technical reference manual provides descriptions of all the functional modules for this series of products. For detailed information on the specific features of a particular model (i.e., the functionality it supports), please refer to the corresponding datasheet.

The data sheet information is as follows:

CMS32M67xx: CMS32M67xx Datasheet\_vx.x.x.pdf

Typically, in the early stages of chip selection, the datasheet should be reviewed first to assess whether the product meets the functional requirements of the design. Once the required product is preliminarily selected, the technical reference manual should be consulted to confirm whether the operating modes of the functional modules meet the requirements. When the selection process moves into the programming and design phase, the technical reference manual should be studied in detail to understand the specific implementation methods and register configurations of each function. For hardware design, the datasheet can be referenced for information on voltage, current, drive capability, pin assignments, and other details.

For detailed information regarding the Cortex-M0+ core, SysTick timer, and NVIC (Nested Vector Interrupt Controller), please refer to the corresponding ARM documentation.

www.mcu.com.cn 2 / 527 Rev.1.0.1

### **Table of Contents**

| Docum  | entation Instructions                                          | 2  |

|--------|----------------------------------------------------------------|----|

| Chapte | r 1 CPU                                                        | 16 |

| 1.1    | Overview                                                       | 16 |

| 1.2    | Cortex-M0+ Core Features                                       | 16 |

| 1.3    | Debugging Features                                             | 16 |

| 1.4    | SWD Interface Pins                                             | 18 |

| 1.5    | ARM Reference Documents                                        | 19 |

| Chapte | r 2 Pin Functions (GPIO)                                       | 20 |

| 2.1    | Port Functions                                                 | 20 |

| 2.2    | Port Alternate Function                                        | 20 |

| 2.3    | Register Mapping                                               | 23 |

| 2.3.1  | Control Function Register Mapping                              | 23 |

| 2.3.2  | Output-Input Alternate Function Register Mapping               | 25 |

| 2.3.3  | Special Function Port RESINB Control Register Mapping          | 27 |

| 2.4    | Register Description                                           | 28 |

| 2.4.1  | Port Register (Px)                                             | 29 |

| 2.4.2  | Port Mode Register (PMx)                                       | 30 |

| 2.4.3  | Pull-Up Resistor Selection Register (PUx)                      | 31 |

| 2.4.4  | Pull-Down Resistor Selection Register (PDx)                    | 32 |

| 2.4.5  |                                                                |    |

| 2.4.6  | 8 ( )                                                          |    |

| 2.4.7  |                                                                |    |

| 2.4.8  | 8 ( )                                                          |    |

| 2.4.9  |                                                                |    |

| 2.4.1  |                                                                |    |

| 2.4.1  |                                                                |    |

| 2.4.1  | 2 Special Function Port RESINB Description (RSTM)              | 43 |

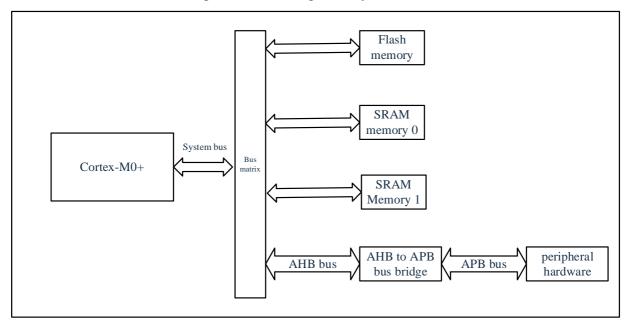

| Chapte | r 3 System Architecture                                        | 44 |

| 3.1    | Overview                                                       | 44 |

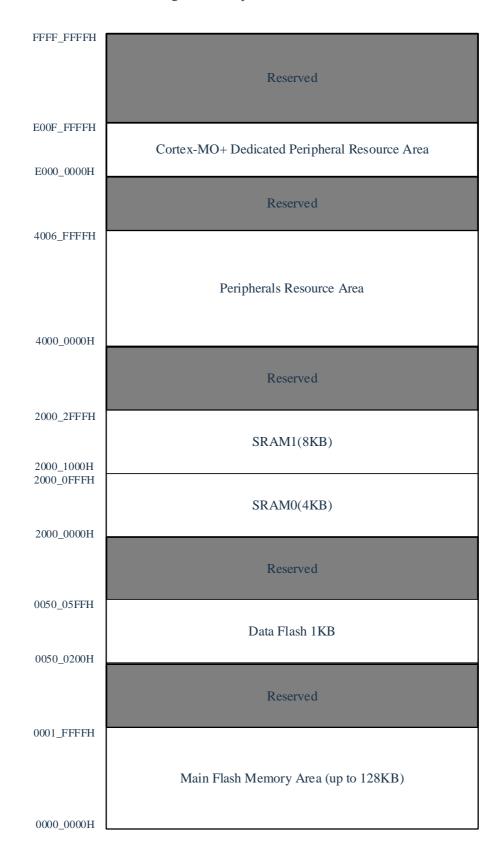

| 3.2    | System Address Partitioning                                    | 45 |

| Chapte | r 4 Clock Generation Circuit                                   | 48 |

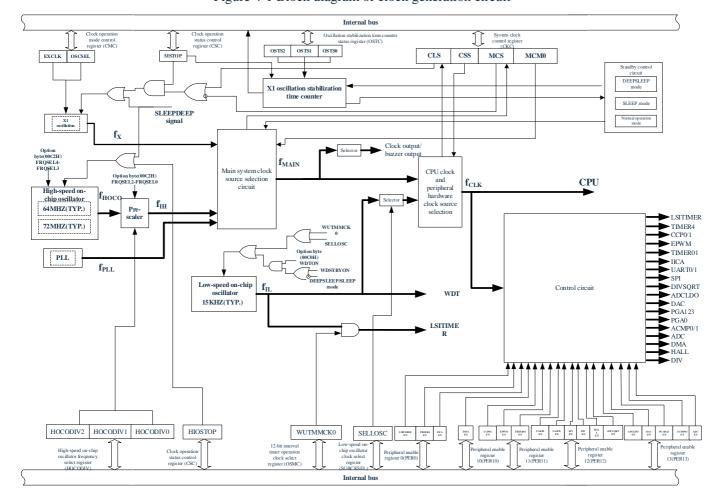

| 4.1    | Functions of Clock Generation Circuit                          | 48 |

| 4.2    | Configuration of Clock Generation Circuit                      | 49 |

| 4.3    | Register Mapping                                               | 51 |

| 4.4    | Register Description                                           | 52 |

| 4.4.1  | System Clock Control Register (CKC)                            | 52 |

| 4.4.2  | Clock Operation Status Control Register (CSC)                  | 53 |

| 4.4.3  | PLL Control Register (PLLCR)                                   | 53 |

| 4.4.4  |                                                                |    |

| 4.4.5  |                                                                |    |

| 4.4.6  |                                                                |    |

| 4.4.7  |                                                                |    |

| 4.4.8  | Peripheral Enable Registers (PER0, PER10, PER11, PER12, PER13) | 58 |

| 4.4   | 12-Bit Interval Timer Operation Clock Selection Register (OSMC)        | 61         |

|-------|------------------------------------------------------------------------|------------|

| 4.4   | 0 High-Speed On-Chip Oscillator Frequency Selection Register (HOCODIV) | 61         |

| 4.4   | 1 Low-Speed On-Chip Oscillator Clock Selection Register (SUBCKSEL)     | 62         |

| 4.4   | 2 Power Supply Mode Control Protection Register (PMUKEY)               | 62         |

| 4.4   | 3 Power Supply Mode Control Register (PMUCTL)                          | 62         |

| 4.5   | System Clock Oscillation Circuit                                       | 63         |

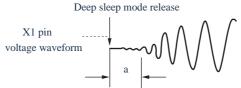

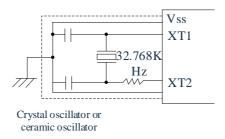

| 4.5   | X1 Oscillation Circuit                                                 | 63         |

| 4.5   | High-Speed On-Chip Oscillator                                          | 63         |

| 4.5   | Low-Speed On-Chip Oscillator                                           | 64         |

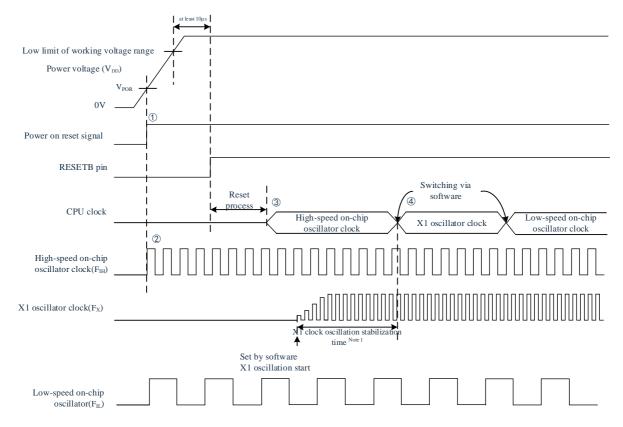

| 4.6   | Operation of Clock Generation Circuit                                  | 65         |

| 4.7   | Clock Control                                                          | 67         |

| 4.7   | Example of Setting Up a High-Speed On-Chip Oscillator                  | 67         |

| 4.7   | Example of Setting X1 Oscillation Circuit                              | 68         |

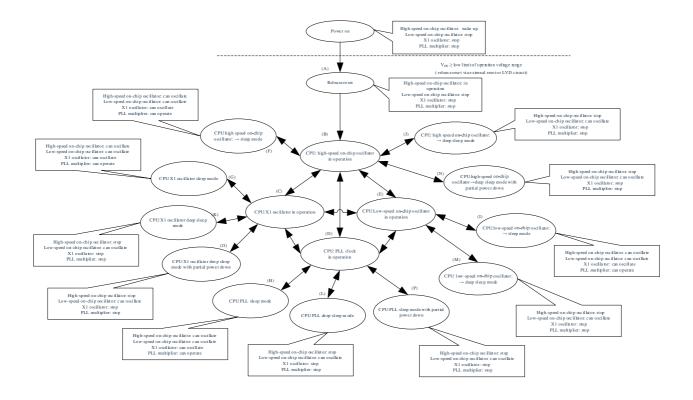

| 4.7   | State Transition Graph of the CPU Clock                                | 69         |

| 4.7   | Conditions Before CPU Clock Transfer and Post-Transfer Processing      | 72         |

| 4.7   | Time Required To Switch CPU Clock and Main System Clock                | 73         |

| 4.7   |                                                                        |            |

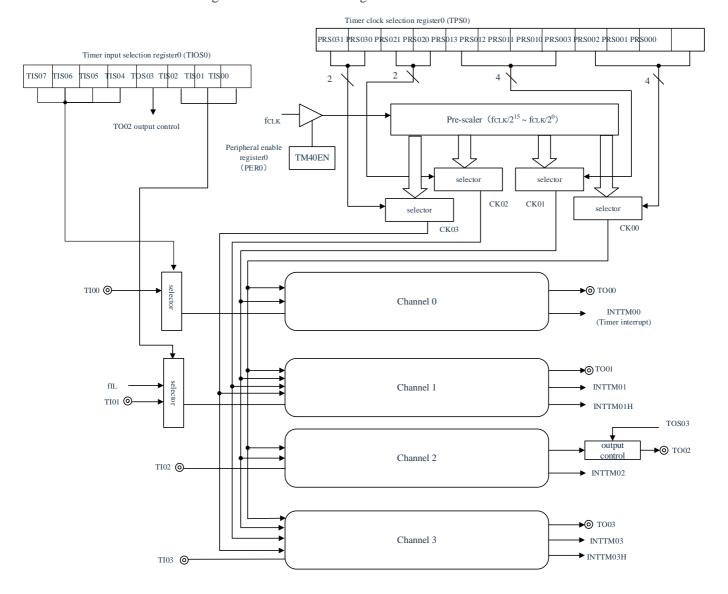

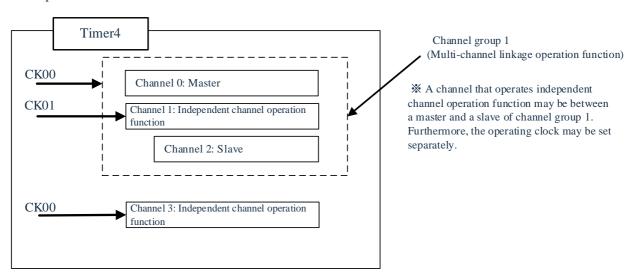

| Chapt | r 5 Universal Timer Unit                                               | <b>7</b> 4 |

| _     | Functions of Universal Timer Unit                                      |            |

| 5.1   |                                                                        |            |

| 5.1   | •                                                                      |            |

| 5.1   | •                                                                      |            |

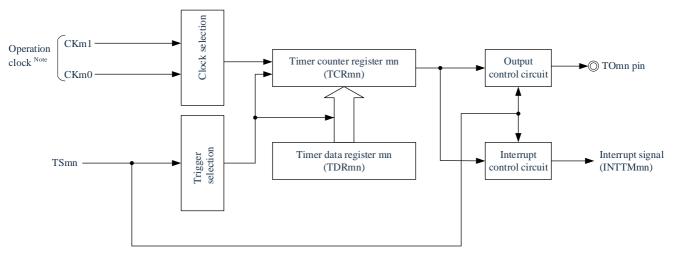

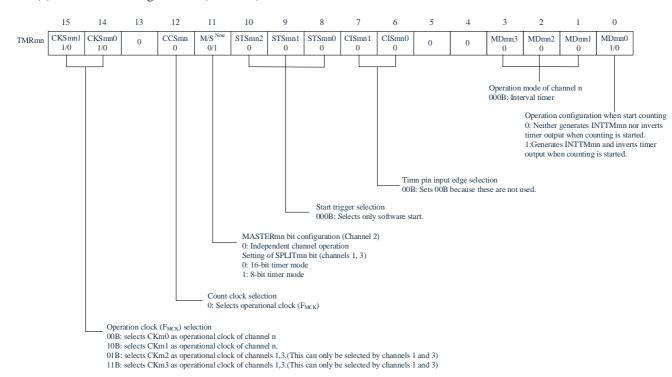

|       | Structure of Universal Timer Unit                                      |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

| 5.2   |                                                                        |            |

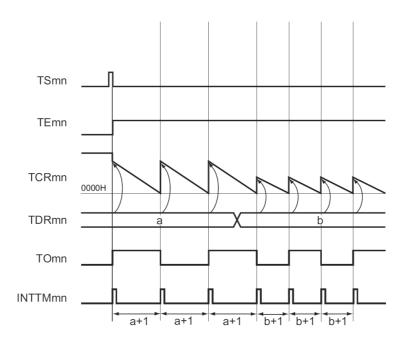

|       | Basic Rules of Universal Timer Unit                                    |            |

| 5.3   |                                                                        |            |

| 5.3   | <u> </u>                                                               |            |

|       | Operation of Counter                                                   |            |

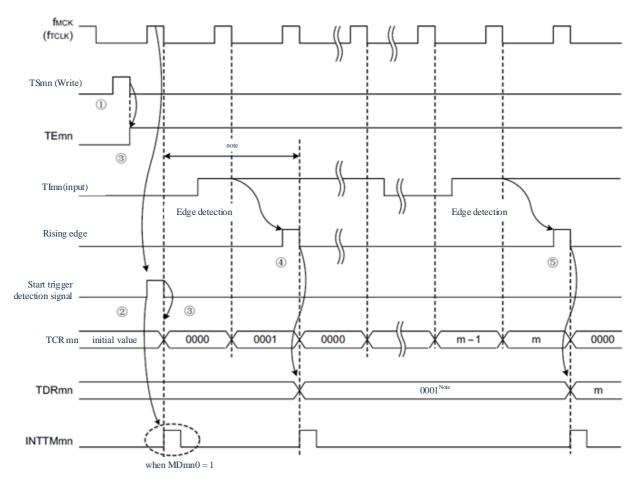

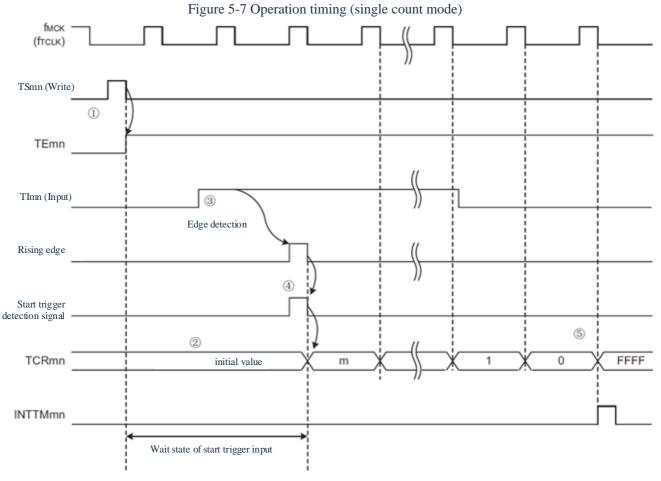

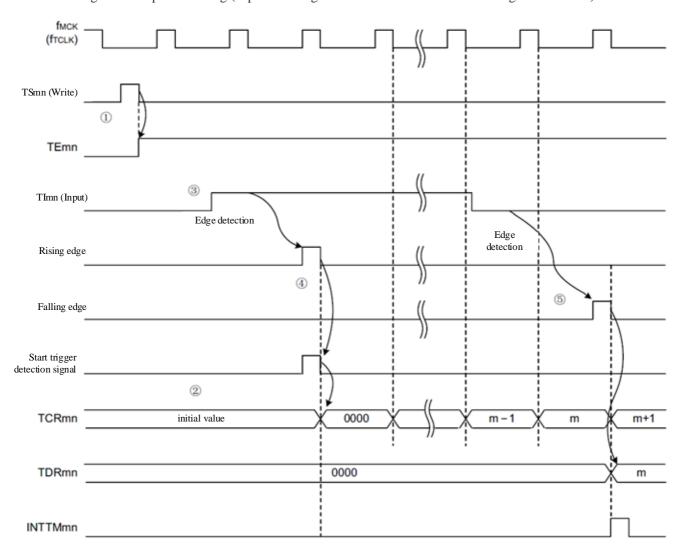

| 5.4   |                                                                        |            |

| 5.4   |                                                                        |            |

| 5.4   |                                                                        |            |

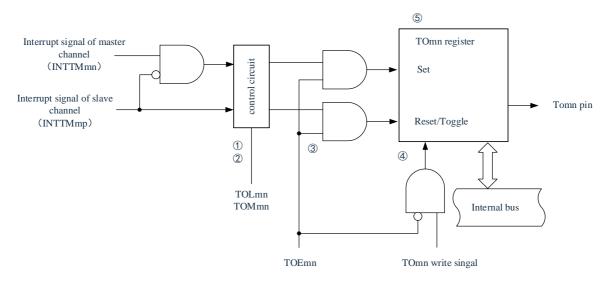

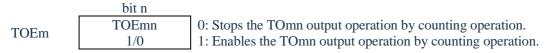

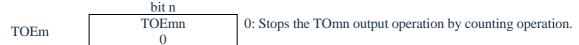

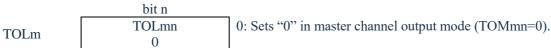

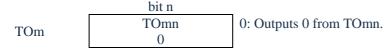

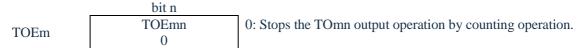

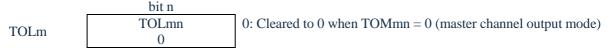

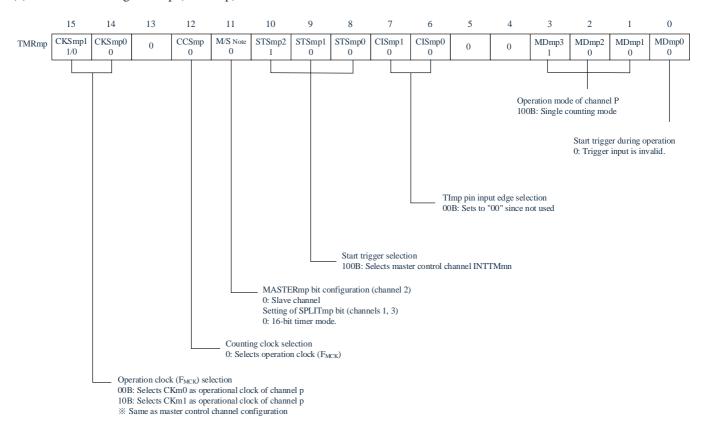

| 5.5   | Channel Output (TOmn Pin) Control                                      |            |

| 5.5   | Chambi Cuput (10hii 1 hi) Collion                                      | 11.        |

| 5.   | 5.1 Tomn Pin Output Circuit Configuration                                              | 115 |

|------|----------------------------------------------------------------------------------------|-----|

| 5.   | 5.2 TOmn Pin Output Setting                                                            | 116 |

| 5.   | 5.3 Cautions on Channel Output Operation                                               | 117 |

| 5.   | 5.4 One-Shot Operation of TOmn Bit                                                     |     |

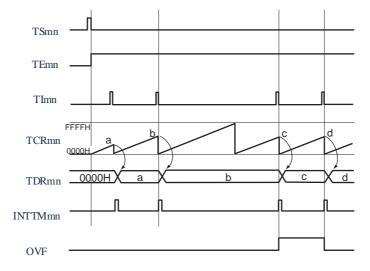

| 5.   | 5.5 Timer Interrupt and TOmn Pin Output When Counting Starts                           | 123 |

| 5.6  | Control of Timer Input (TImn)                                                          | 124 |

| 5.   | 6.1 Structure of TImn Pin Input Circuit                                                | 124 |

| 5.   | 6.2 Cautions on Channel Input Operation                                                | 124 |

| 5.7  | Independent Channel Operation Function of Universal Timer Unit                         |     |

| 5.   | 7.1 Operation as Interval Timer/Square Wave Output                                     | 125 |

| 5.   | 7.2 Operation as External Event Counter                                                | 129 |

| 5.   | 7.3 Operation as Frequency Divider                                                     |     |

| 5.   | 7.4 Operation as Input Pulse Interval Measurement                                      |     |

| _    | 7.5 Operation as Input Signal High-/Low-Level Width Measurement                        |     |

|      | 7.6 Operation as Delay Counter                                                         |     |

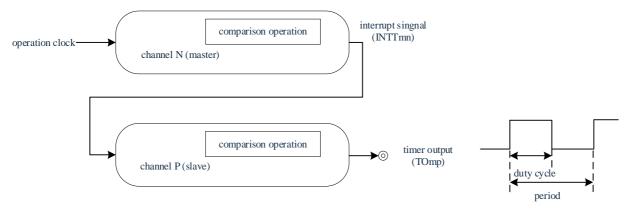

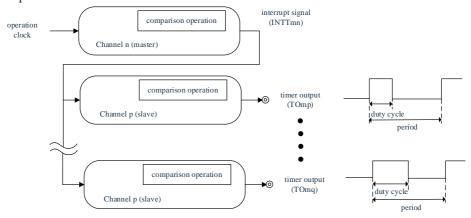

|      | Multi-Channel Linkage Operation Function for Universal Timer Unit                      |     |

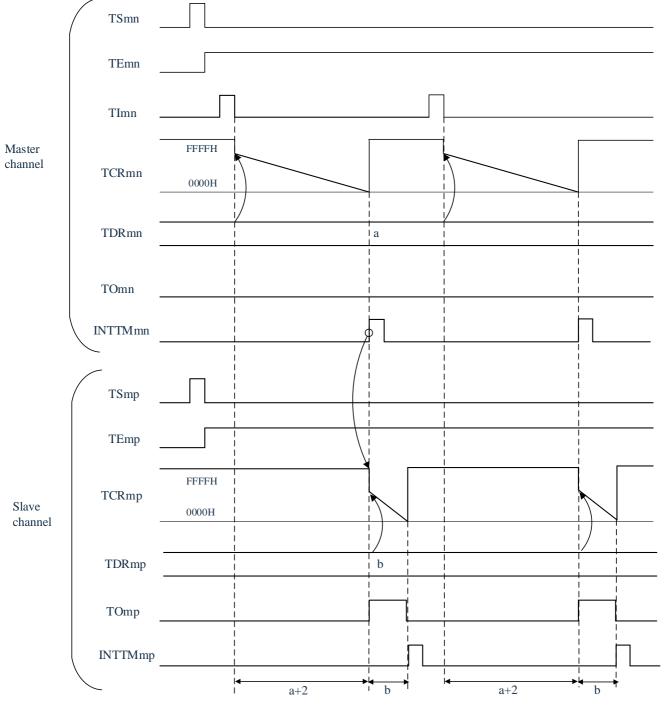

|      | 8.1 Operation as Single Trigger Pulse Output Function                                  |     |

|      | 8.2 Operation as PWM Function                                                          |     |

| 5.   | 8.3 Operation as Multiple PWM Output Function                                          | 161 |

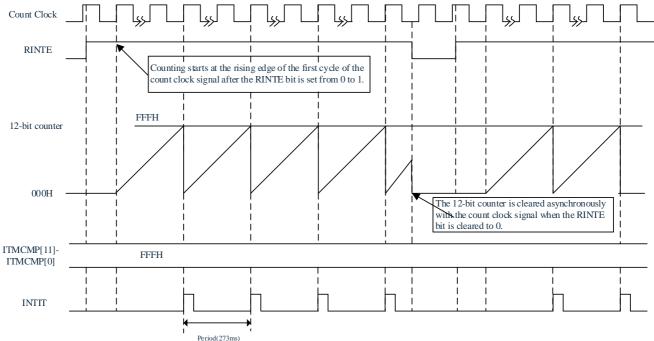

| Chap | oter 6 LSITIMER 12-Bit Interval Timer                                                  | 169 |

| 6.1  | Functions of 12-Bit Interval Timer                                                     | 169 |

| 6.2  | Configuration of 12-Bit Interval Timer                                                 | 169 |

| 6.3  | Register Mapping                                                                       | 169 |

| 6.4  | 12-Bit Interval Timer Control Register (CON0)                                          | 169 |

| 6.5  | 12-Bit Interval Timer Operation                                                        | 171 |

| 6.   | 5.1 12-Bit Interval Timer Operation Timing                                             | 171 |

| 6.   | 5.2 Start of Count Operation and Re-Enter to Sleep Mode After Returned From Sleep Mode | 172 |

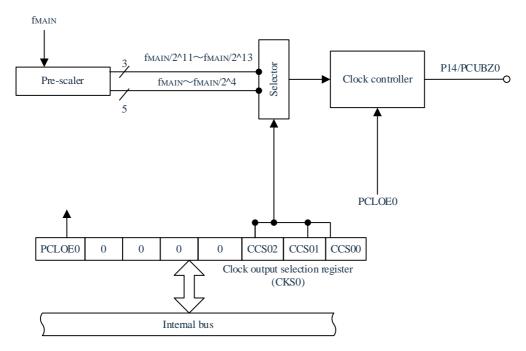

| Char | oter 7 Clock Output Controller                                                         | 173 |

| _    | Functions of Clock Output Controller                                                   |     |

| 7.1  | •                                                                                      |     |

| 7.2  |                                                                                        |     |

|      | 3.1 Clock Output Selection Register (CKS0)                                             |     |

| 7.4  |                                                                                        |     |

| 7.5  |                                                                                        |     |

|      | 5.1 Operation as Output Pin                                                            |     |

|      | Cautions of Clock Output/Buzzer Output Controller                                      |     |

|      |                                                                                        |     |

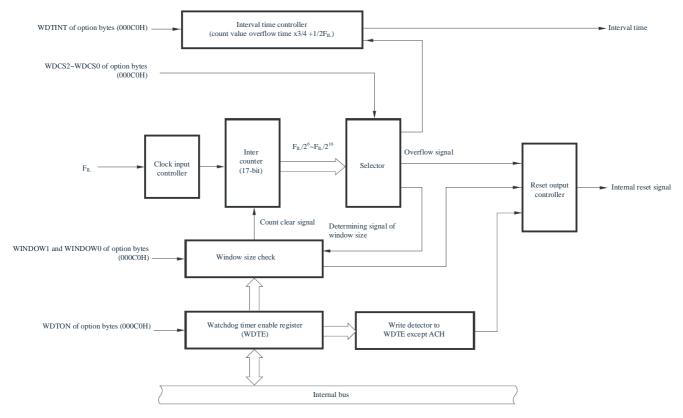

| Cnap | oter 8 Watchdog Timer (WDT)                                                            |     |

| 8.1  | č                                                                                      |     |

| 8.2  |                                                                                        |     |

| 8.3  |                                                                                        |     |

|      | 3.1 Watchdog Timer Enable Register (WDTE)                                              |     |

|      | 3.2 LOCKUP Control Register (LOCKCTL)                                                  |     |

|      | 3.3 Protection Register (PRCR)                                                         |     |

|      | 3.4 Watchdog Configuration Register WDTCFGx (x=0~3)                                    |     |

| 8.4  | Operation of Watchdog Timer                                                            | 183 |

| 8.4.1      | Operational Control of Watchdog Timer             | 183 |

|------------|---------------------------------------------------|-----|

| 8.4.2      | Setting Overflow Time of Watchdog Timer           | 184 |

| 8.4.3      | Setting Window Open Period of Watchdog Timer      | 185 |

| 8.4.4      | Setting Watchdog Timer Interval Interrupt         | 186 |

| 8.4.5      | Operation of Watchdog Timer During LOCKUP         | 186 |

| Chapter 9  | Division and Square Root Operation Unit (DIVSQRT) | 187 |

| 9.1 Ove    | rview                                             | 187 |

| 9.2 Feat   | ures                                              | 187 |

| 9.3 Fun    | ction Description                                 | 187 |

| 9.4 Reg    | ister Mapping                                     | 188 |

| 9.5 Reg    | ister Description                                 | 189 |

| 9.5.1      | DIVSQRT Control Register (CON)                    | 189 |

| 9.5.2      | DIVSQRT Data A Register (ALUA)                    | 189 |

| 9.5.3      | DIVSQRT Data B Register (ALUB)                    | 189 |

| 9.5.4      | DIVSQRT Result 0 Register (RES0)                  | 189 |

| 9.5.5      | DIVSQRT Result 1 Register (RES1)                  | 189 |

| Chapter 10 | Division Operation Unit (DIV)                     | 190 |

| 10.1 Ove   | rview                                             | 190 |

| 10.2 Feat  | ures                                              | 190 |

| 10.3 Fund  | ction Description                                 | 190 |

| 10.4 Reg   | ister Mapping                                     | 190 |

| 10.5 Reg   | ister Description                                 | 191 |

| 10.5.1     | Division Control Register (CON)                   | 191 |

| 10.5.2     | Division Data A Register (ALUA)                   | 191 |

| 10.5.3     | Division Data B Register (ALUB)                   |     |

| 10.5.4     | Division Result 0 Register (RES0)                 |     |

| 10.5.5     | Division Result 1 Register (RES1)                 | 191 |

| Chapter 11 | Timer (TIMER0/1)                                  | 192 |

| 11.1 Ove   | rview                                             | 192 |

| 11.2 Feat  | ures                                              | 192 |

| 11.3 Fun   | ction Description                                 |     |

| 11.3.1     | One-Shot Trigger Mode                             | 192 |

| 11.3.2     | Periodic Count Mode                               |     |

| 11.3.3     | Continuous Count Mode                             |     |

| 11.3.4     | Delayed Load Function                             |     |

| _          | ister Mapping                                     |     |

| C          | ister Description                                 |     |

| 11.5.1     | Timer Control Register (CON0/1)                   |     |

| 11.5.2     | Timer Load Register (LOAD0/1)                     |     |

| 11.5.3     | Timer Current Value Register (VAL0/1)             |     |

| 11.5.4     | Timer Interrupt Source Status Register (RISO/1)   |     |

| 11.5.5     | Timer Enabled Interrupt Status Register (MIS0/1)  |     |

| 11.5.6     | Timer Interrupt Clear Register (ICLR0/1)          |     |

| 11.5.7     | Timer Delayed Load Register (BGLOAD0/1)           |     |

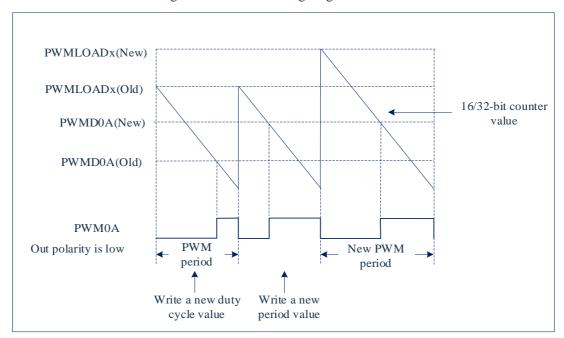

| Chapter 12 | 2 Capture/Compare/PWM Module (CCP0/1)             | 196 |

| 12.1 Ove  | erview                                         | 196 |

|-----------|------------------------------------------------|-----|

| 12.2 Fea  | tures                                          | 196 |

| 12.3 Fur  | nction Description                             | 197 |

| 12.3.1    | Pulse Width Modulation (PWM)                   | 197 |

| 12.3.2    | Square Wave Output Mode                        | 198 |

| 12.3.3    | Capture Mode 0                                 | 198 |

| 12.3.4    | Capture Mode 1                                 | 199 |

| 12.3.5    | Capture Mode 2                                 | 201 |

| 12.3.6    | PWM Configuration Process                      | 202 |

| 12.3.7    | Interrupt                                      | 202 |

| 12.4 Reg  | gister Mapping                                 | 203 |

| 12.5 Reg  | gister Description                             | 204 |

| 12.5.1    | CCP0 Control Register (CCP0CON)                | 204 |

| 12.5.2    | CCP0 Reload Register (CCP0LOAD)                |     |

| 12.5.3    | CCP0A Data Register (CCP0DA)                   |     |

| 12.5.4    | CCP0B Data Register (CCP0DB)                   | 205 |

| 12.5.5    | CCP1 Control Register (CCP1CON)                | 206 |

| 12.5.6    | CCP1 Reload Register (CCP1LOAD)                |     |

| 12.5.7    | CCP1A Data Register (CCP1DA)                   |     |

| 12.5.8    | CCP1B Data Register (CCP1DB)                   |     |

| 12.5.9    | CCP Interrupt Enable Register (CCPIMSC)        |     |

| 12.5.10   | CCP Interrupt Source Status Register (CCPRIS)  |     |

| 12.5.11   | CCP Enabled Interrupt Status Register (CCPMIS) |     |

| 12.5.12   |                                                |     |

| 12.5.13   | CCP Operation Register (CCPRUN)                |     |

| 12.5.14   |                                                |     |

| 12.5.15   |                                                |     |

| 12.5.16   |                                                |     |

| 12.5.17   |                                                |     |

| 12.5.18   | CCP1 CAP Control Register 3 (CAPCON3)          |     |

|           | CCP1 CAP0 Data Register (CAP0DATA)             |     |

| 12.5.20   | CCP1 CAPn Data Register (CAPnDATA) (n=1-3)     | 214 |

| 12.5.21   |                                                |     |

| Chapter 1 |                                                |     |

| _         | erview                                         |     |

|           | utures                                         |     |

|           | action Description                             |     |

| 13.3.1    | Block Diagram                                  |     |

| 13.3.1    | Clock Division                                 |     |

| 13.3.2    |                                                |     |

|           | Signal Input Filter                            |     |

| 13.3.4    |                                                |     |

| 13.3.5    | Capture                                        |     |

|           | gister Mapping.                                |     |

|           | gister Description                             |     |

| 13.5.1    | HALL Module Configuration Register (CFG)       |     |

| 13.5.2    | HALL Module Information Register (INFO)        |     |

| 13.5.3    | HALL Message Clear Register (CLRF)             | 220 |

| 13.5.4    | HALL Module Width Counter Value Register (WIDTH)         | 220 |

|-----------|----------------------------------------------------------|-----|

| 13.5.5    | HALL Module Counter Threshold Value Register (TH)        | 220 |

| 13.5.6    | HALL Counter Register (CNT)                              | 220 |

| 13.5.7    | HALL Write Enable Register (LOCK)                        | 220 |

| Chapter 1 | Enhanced PWM(EPWM)                                       | 221 |

| 14.1 Ove  | rview                                                    | 221 |

| 14.2 Feat | tures                                                    | 221 |

| 14.3 Fun  | ction Description                                        | 222 |

| 14.3.1    | Block Diagram                                            | 223 |

| 14.3.2    | Clock Division                                           | 223 |

| 14.3.3    | Independent Output Mode                                  | 223 |

| 14.3.4    | Complementary Output Mode                                | 224 |

| 14.3.5    | Synchronous Output Mode                                  | 224 |

| 14.3.6    | Group Output Mode                                        | 225 |

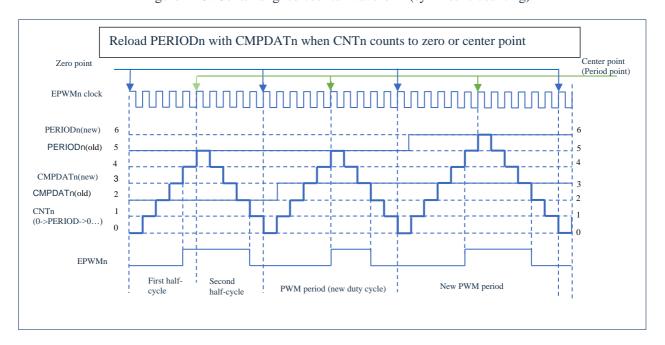

| 14.3.7    | Load Update Mode                                         | 226 |

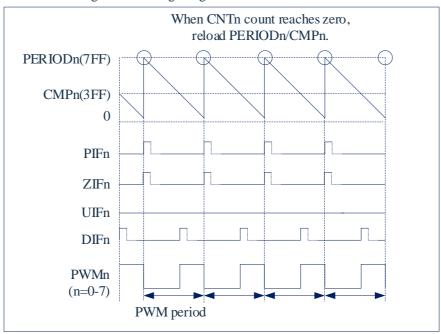

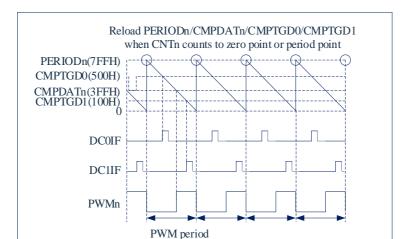

| 14.3.8    | Edge-Aligned Counting Mode                               | 228 |

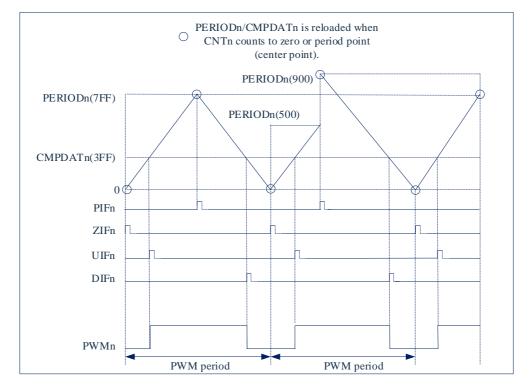

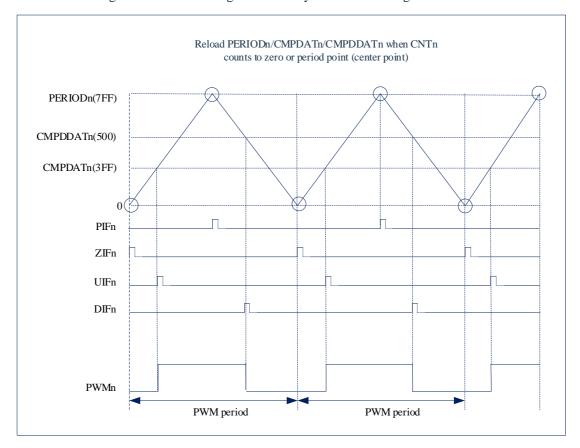

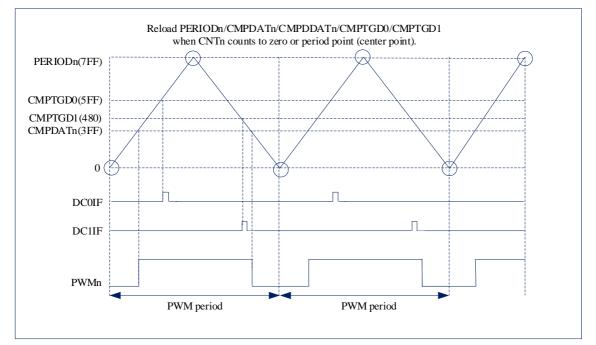

| 14.3.9    | Center-Aligned Counting Mode                             | 229 |

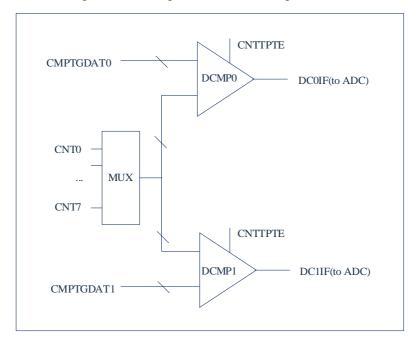

| 14.3.10   | Independent Counter Compare Function                     | 232 |

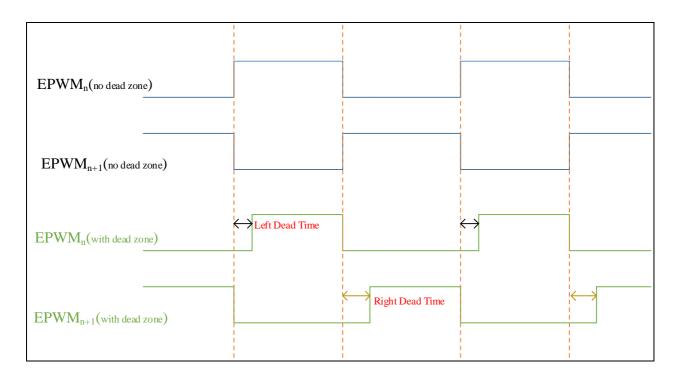

| 14.3.11   | Programmable Dead-Time Generator                         | 234 |

| 14.3.12   | Mask and Mask Preset Function                            | 235 |

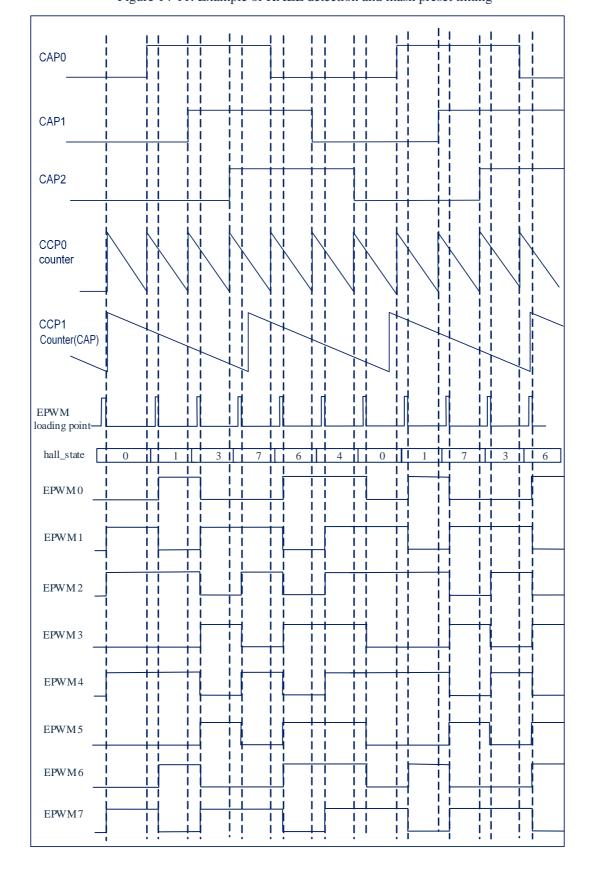

| 14.3.13   | Hall Sensor Interface Function.                          | 235 |

| 14.3.14   | Fault Protection Function (Brake and Recovery Function)  | 238 |

| 14.3.15   | Output Status in Debug Mode                              | 240 |

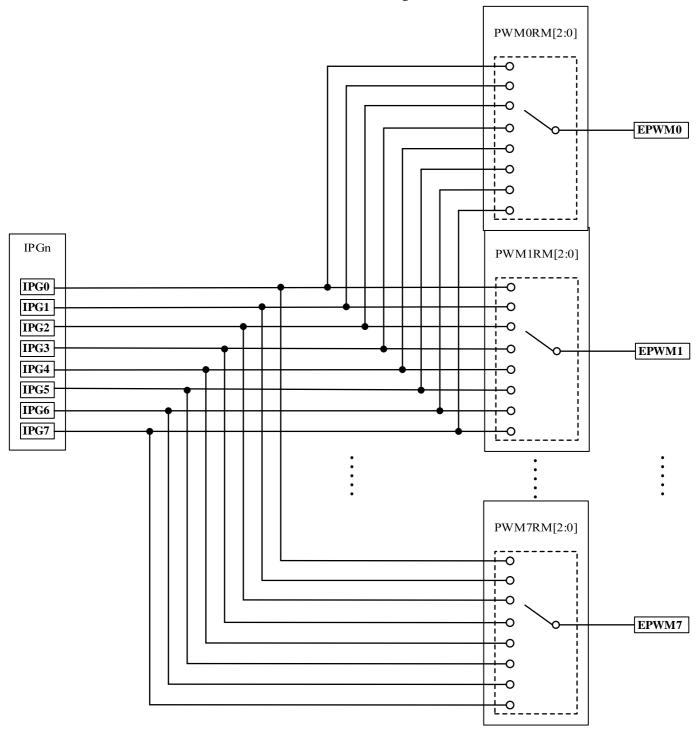

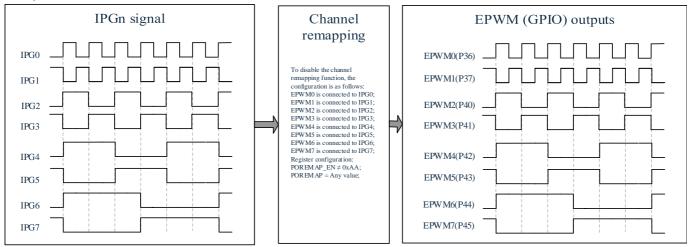

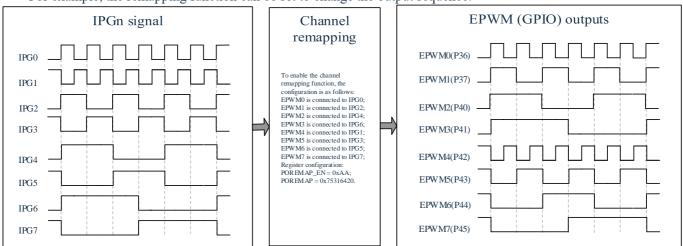

| 14.3.16   | Output Channel Remapping Function                        | 241 |

| 14.3.17   | EPWM Configuration Process                               | 243 |

| 14.3.18   | Interrupt                                                | 243 |

| 14.4 Reg  | ister Mapping                                            | 244 |

| 14.5 Reg  | ister Description                                        | 246 |

| 14.5.1    | EPWM Prescaler Register (CLKPSC)                         | 246 |

| 14.5.2    | EPWM Clock Selection Register (CLKDIV)                   | 247 |

| 14.5.3    | EPWM Control Register (CON)                              | 249 |

| 14.5.4    | EPWM Control Register (CON2)                             | 251 |

| 14.5.5    | EPWM Control Register (CON3)                             | 252 |

| 14.5.6    | EPWM Control Register (CON4)                             | 255 |

| 14.5.7    | EPWM Period Register 0-7 (PERIOD0-7)                     | 255 |

| 14.5.8    | EPWM Compare Register 0-7 (CMPDAT0-7)                    | 255 |

| 14.5.9    | EPWM Output Control Register (POEN)                      | 256 |

| 14.5.10   | EPWM Output Channel Remap Enable Register 1 (POREMAP_EN) | 256 |

| 14.5.11   | EPWM Output Channel Remap Register (POREMAP)             | 257 |

| 14.5.12   | EPWM Fault Protection Control Register (BRKCTL)          | 259 |

| 14.5.13   | EPWM Dead Zone Length Register (DTCTL01)                 | 261 |

| 14.5.14   | EPWM Dead Zone Length Register (DTCTL23)                 | 261 |

| 14.5.15   | EPWM Dead Zone Length Register (DTCTL45)                 | 261 |

| 14.5.16   | EPWM Dead Zone Length Register (DTCTL67)                 | 261 |

| 14.5.17   | EPWM Mask Output Control Register (MASK)                 | 262 |

| 14.5.18   | EPWM Mask Output Control Preset Register (MASKNXT)       | 264 |

| 14.5.19   | EPWM Trigger Compare Register (CMPTGD0-1)                | 266 |

| 14.5.20   | EPWM Interrupt Enable Register (IMSC)                  | 266 |

|-----------|--------------------------------------------------------|-----|

| 14.5.21   | EPWM Interrupt Enable Register 2(IMSC2)                | 267 |

| 14.5.22   | EPWM Interrupt Source Status Register (RIS)            | 267 |

| 14.5.23   | EPWM Interrupt Source Status Register 2 (RIS2)         | 268 |

| 14.5.24   | EPWM Enabled Interrupt Status Register (MIS)           | 269 |

| 14.5.25   | EPWM Enabled Interrupt Status Register 2(MIS2)         |     |

| 14.5.26   | EPWM Interrupt Clear Control Register (ICLR)           | 270 |

| 14.5.27   | EPWM Interrupt Clear Control Register 2(ICLR2)         | 270 |

| 14.5.28   | EPWM Interrupt Accumulation Control Register (IFA)     | 271 |

| 14.5.29   | EPWM Write Enable Control Register (LOCK)              | 271 |

| 14.5.30   | EPWM Fault Protection Recovery Delay Register (BRKRDT) | 271 |

| Chapter 1 |                                                        |     |

| 15.1 Fea  | tures                                                  | 273 |

| 15.2 Fun  | ction Description                                      | 273 |

| 15.2.1    | UARTn Function Mode                                    | 273 |

| 15.2.2    | UARTn Interrupt and Status                             | 273 |

| 15.3 Reg  | rister Mapping                                         | 274 |

| 15.4 Reg  | rister Description                                     | 274 |

| 15.4.1    | Receive Buffer Register (RBR)                          |     |

| 15.4.2    | Transmit Buffer Register (THR)                         | 274 |

| 15.4.3    | Baud Rate Divider Register (DLR)                       | 274 |

| 15.4.4    | Interrupt Enable Register (IER)                        |     |

| 15.4.5    | Interrupt Status Register (IIR)                        |     |

| 15.4.6    | Line Control Register (LCR)                            | 276 |

| 15.4.7    | Modem Control Register (MCR)                           | 276 |

| 15.4.8    | Line Status Register (LSR)                             | 277 |

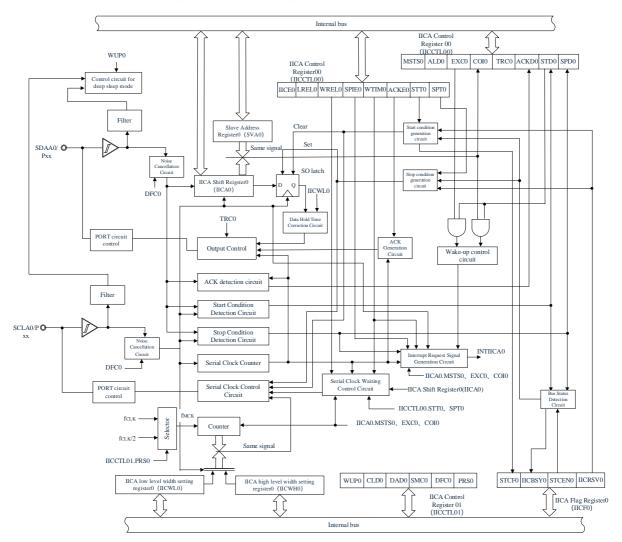

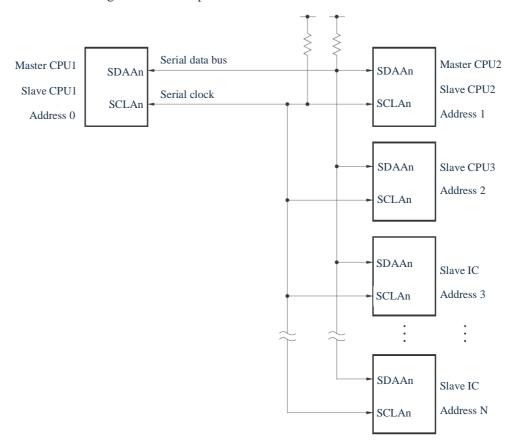

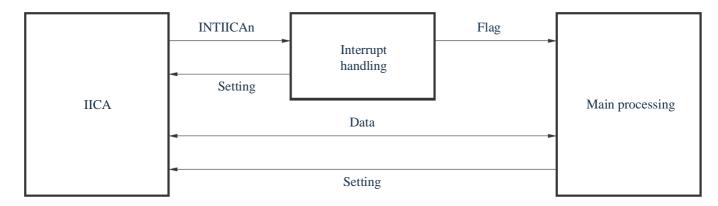

| Chapter 1 | 6 Serial Interface IICA (IICA)                         | 278 |

| 16.1 Fun  | ctions of Serial Interface IICA                        | 278 |

|           | acture of Serial Interface IICA                        |     |

|           | ister Mapping                                          |     |

| _         | risters for Controlling Serial Interface IICA          |     |

| _         | pheral Enable Register 0 (PER0)                        |     |

| 16.5.1    | IICA Control Register n0 (IICCTLn0).                   |     |

| 16.5.2    | IICA Status Register n (IICSn)                         |     |

| 16.5.3    | IICA Flag Register n (IICFn)                           |     |

| 16.5.4    | IICA Control Register n1 (IICCTLn1)                    |     |

| 16.5.5    | IICA Low Level Width Setting Register n (IICWLn)       |     |

| 16.5.6    | IICA High Level Width Setting Register n (IICWHn)      |     |

| 16.5.7    | Registers for Controlling Pin Port Functions of IICA   |     |

|           | ctions of I <sup>2</sup> C Bus Mode                    |     |

| 16.6.1    | Pin Structure                                          |     |

| 16.6.2    | Setting Transfer Clock via IICWLn and IICWHn Registers |     |

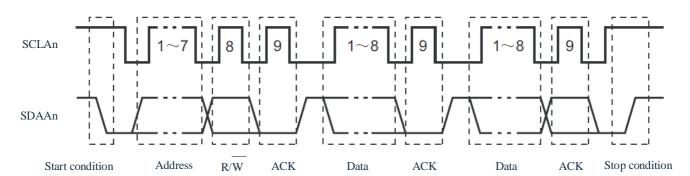

|           | inition and control method of I <sup>2</sup> C bus.    |     |

| 16.7.1    | Start Condition                                        |     |

| 16.7.2    | Address                                                |     |

| 16.7.3    | Transfer Direction Specification                       |     |

|           |                                                        |     |

| 16.7.4     | Acknowledge (ACK)                                                      | 305 |

|------------|------------------------------------------------------------------------|-----|

| 16.7.5     | Stop Condition                                                         | 306 |

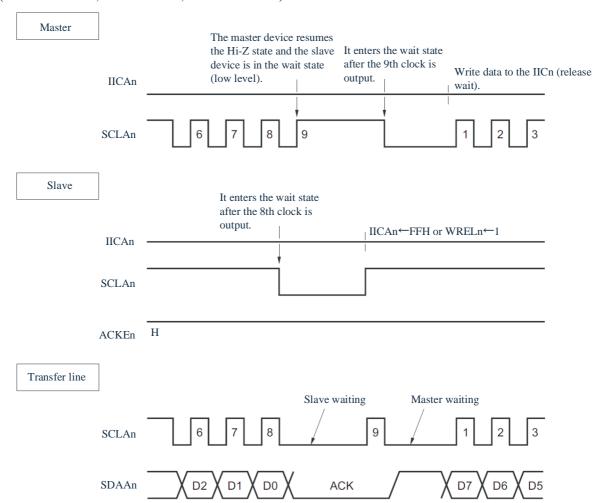

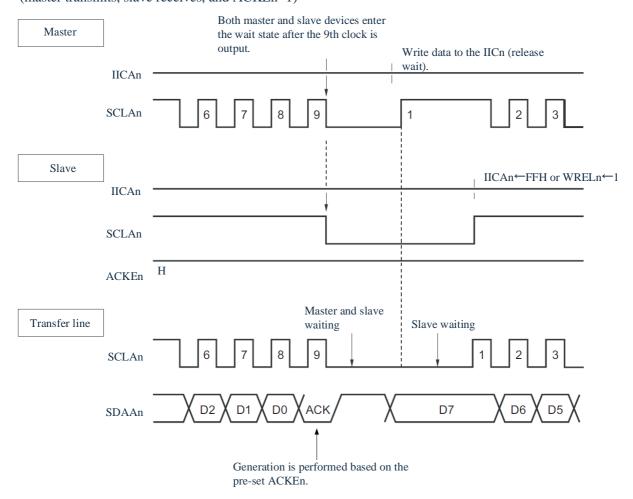

| 16.7.6     | Wait                                                                   | 307 |

| 16.7.7     | Wait Release Methods                                                   | 309 |

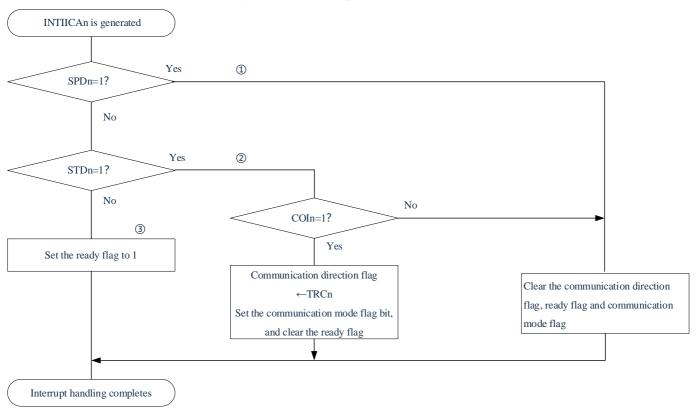

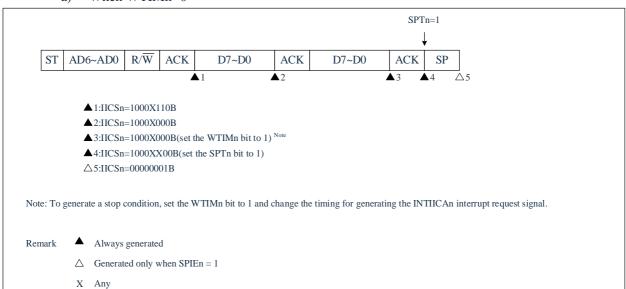

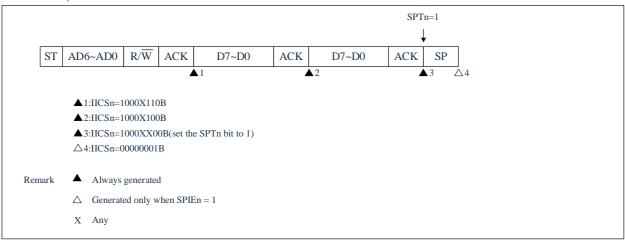

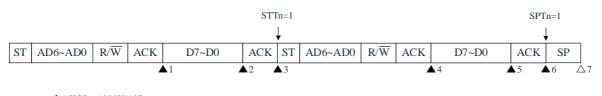

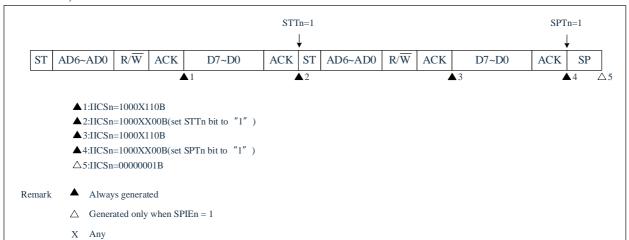

| 16.7.8     | Generation Timing and Waiting Control of Interrupt Requests (INTIICAn) | 310 |

| 16.7.9     | Detection for Address Matching                                         | 312 |

| 16.7.10    | Error Detection                                                        | 312 |

| 16.7.11    | Extension Code                                                         | 313 |

| 16.7.12    | Arbitration                                                            | 314 |

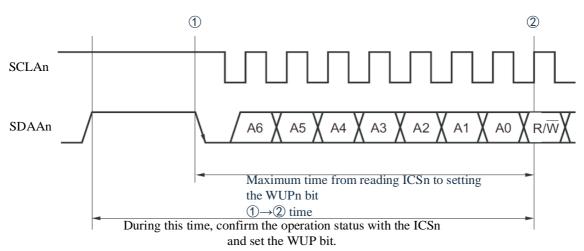

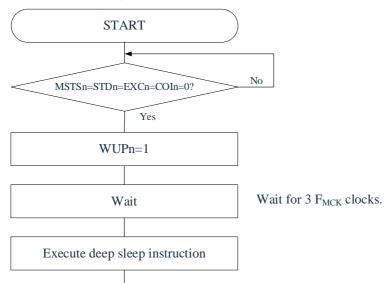

| 16.7.13    | Wake-Up Function                                                       | 316 |

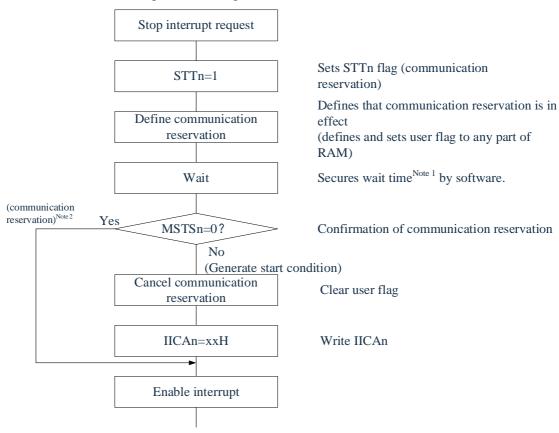

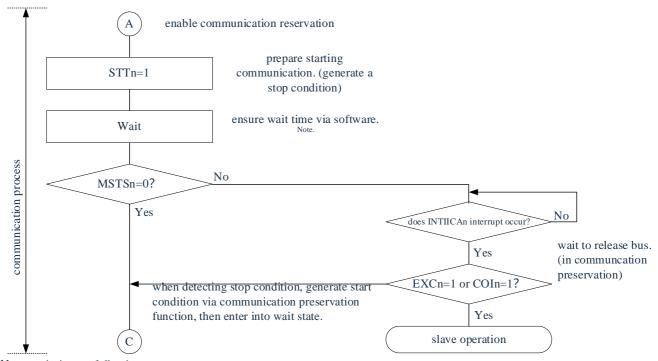

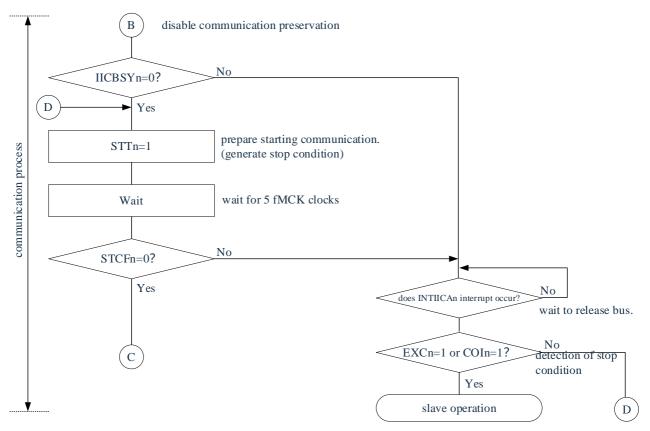

| 16.7.14    | Communication Reservation                                              | 319 |

| 16.7.15    | Cautions                                                               |     |

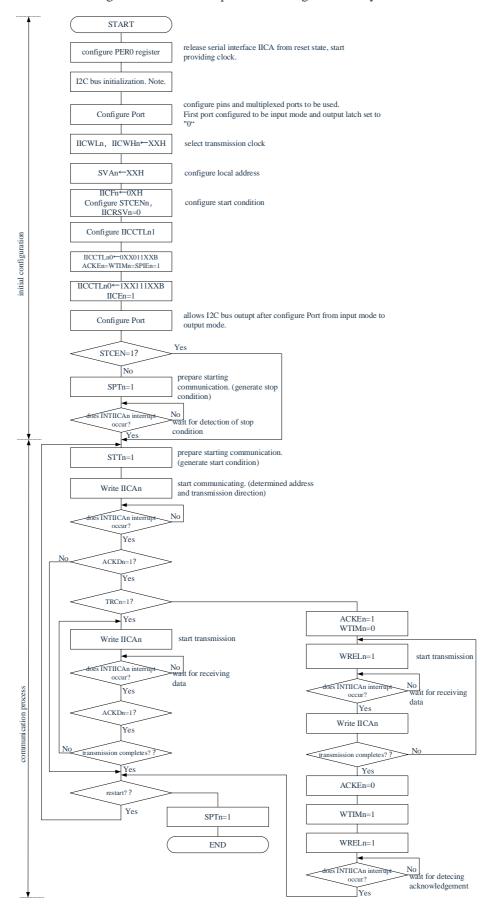

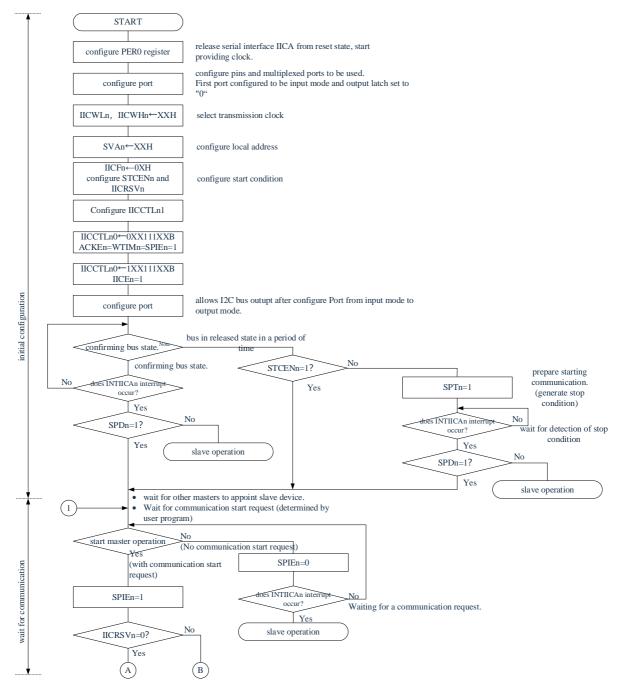

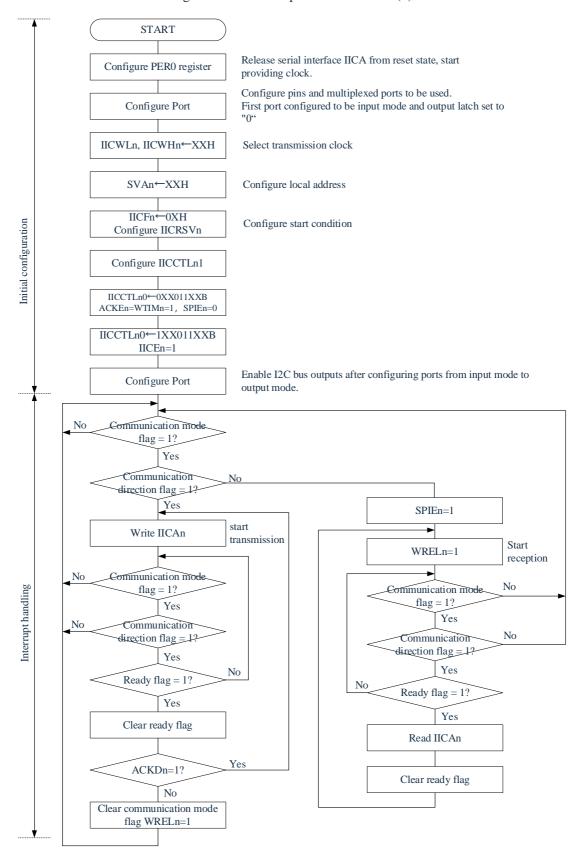

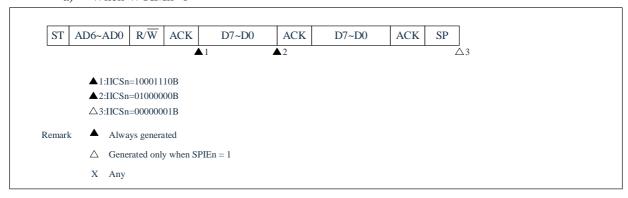

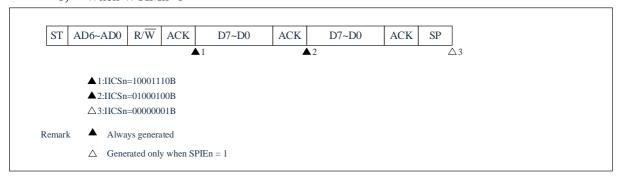

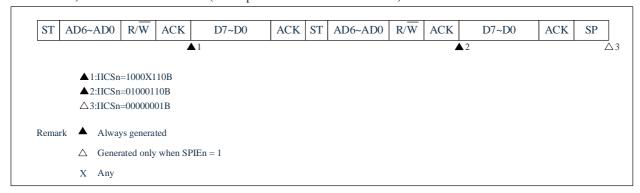

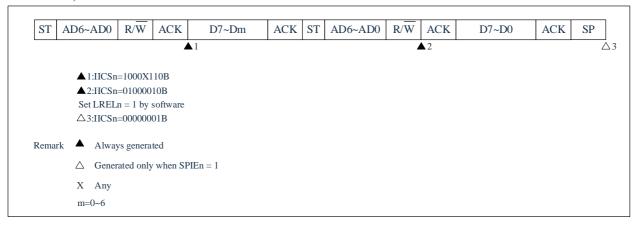

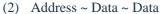

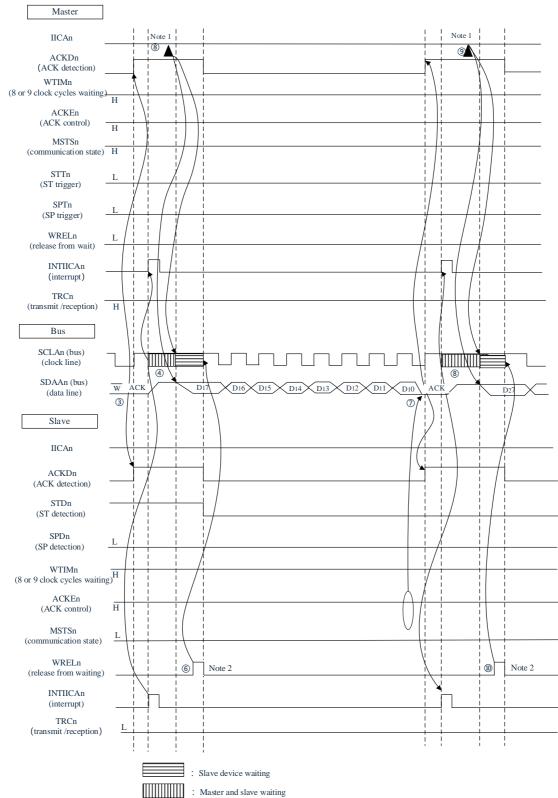

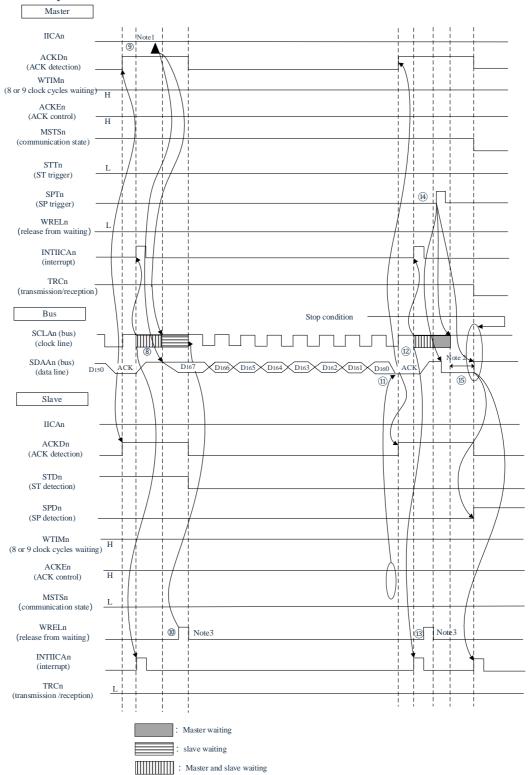

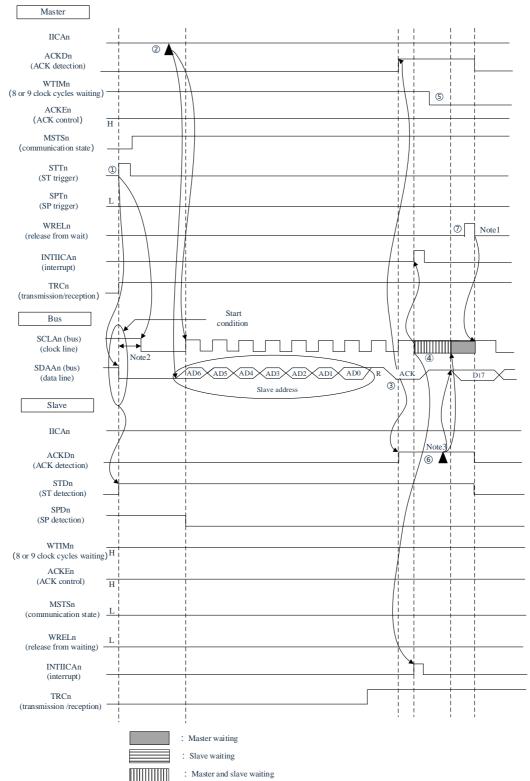

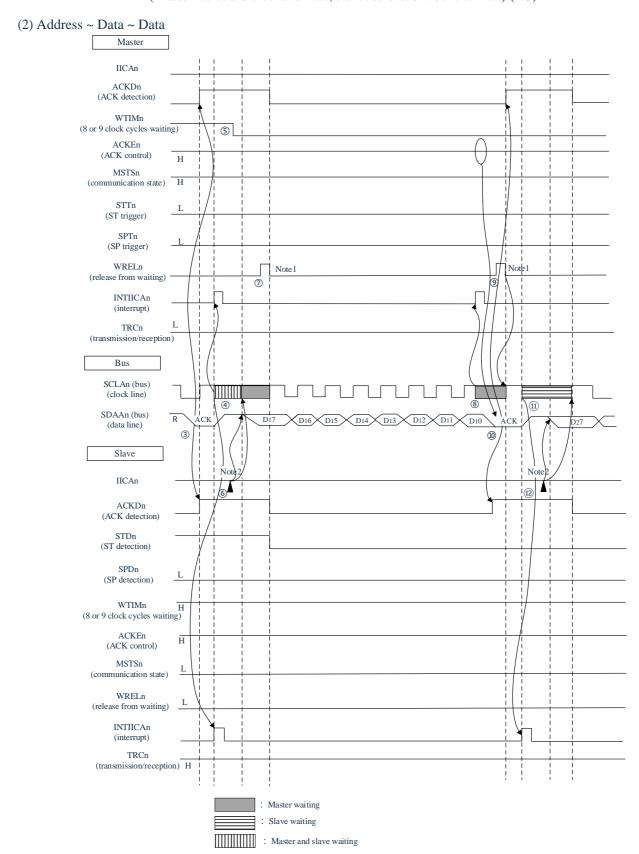

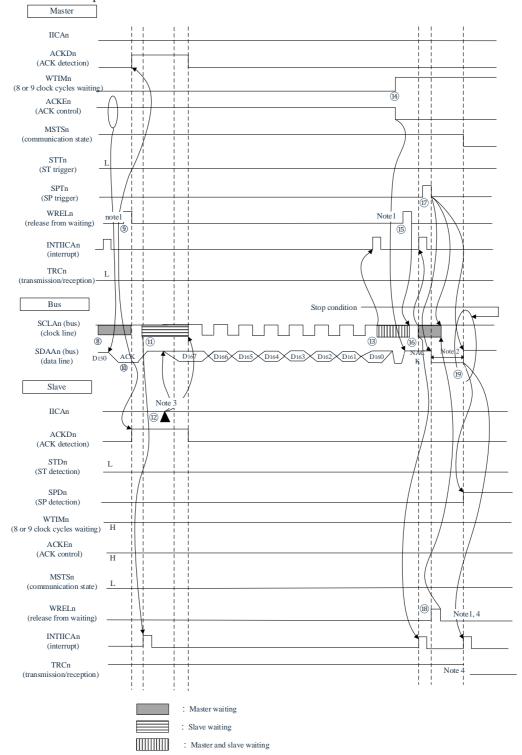

| 16.7.16    | Communication Operation                                                | 324 |

| 16.7.17    | Timing of I <sup>2</sup> C Interrupt Request (INTIICAn) Generation     |     |

| 16.8 Tim   | ing Diagrams                                                           | 353 |

| Chapter 1' | Serial Peripheral Interface Controller (SSP/SPI)                       | 368 |

|            | rview                                                                  |     |

|            | tures                                                                  |     |

| _          | ister Mapping                                                          |     |

| 17.4 Reg   | ister Description                                                      |     |

| 17.4.1     | SSP Control Register (CON)                                             |     |

| 17.4.2     | SSP Status Register (STAT)                                             |     |

| 17.4.3     | SSP Data Register (DAT)                                                |     |

| 17.4.4     | SSP Clock Controller (CLK)                                             |     |

| 17.4.5     | SSP Interrupt Enable Register (IMSC)                                   |     |

| 17.4.6     | SSP Interrupt Source Status Register (RIS)                             |     |

| 17.4.7     | SSP Enabled Interrupt Status Register (MIS)                            |     |

| 17.4.8     | SSP Interrupt Clear Register (ICLR)                                    |     |

| 17.4.9     | SSP Software Chip Select Signal Register (CSCR)                        | 371 |

| Chapter 18 | 8 Enhanced DMA                                                         | 372 |

| 18.1 Fun   | ctions of DMA                                                          | 372 |

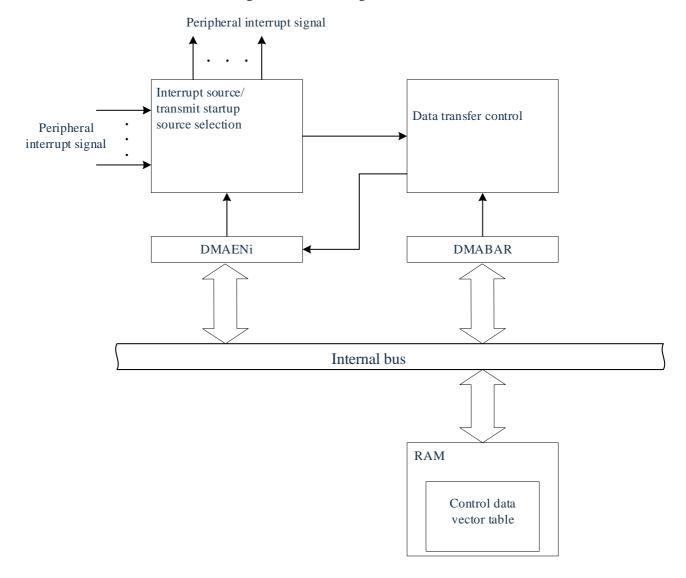

| 18.2 Stru  | icture of DMA                                                          |     |

| 18.3 Reg   | ister Mapping                                                          | 375 |

| 18.4 Reg   | isters for Controlling DMA                                             | 376 |

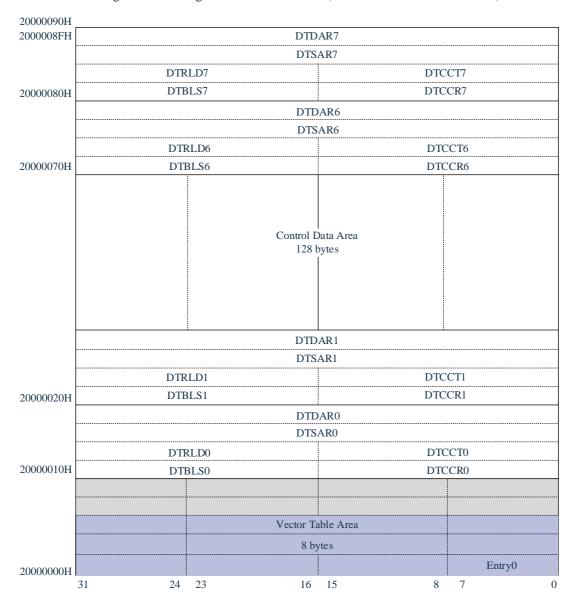

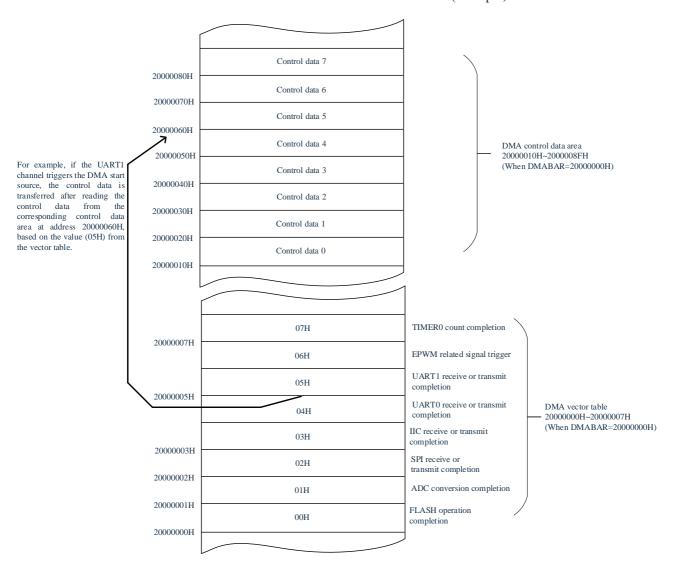

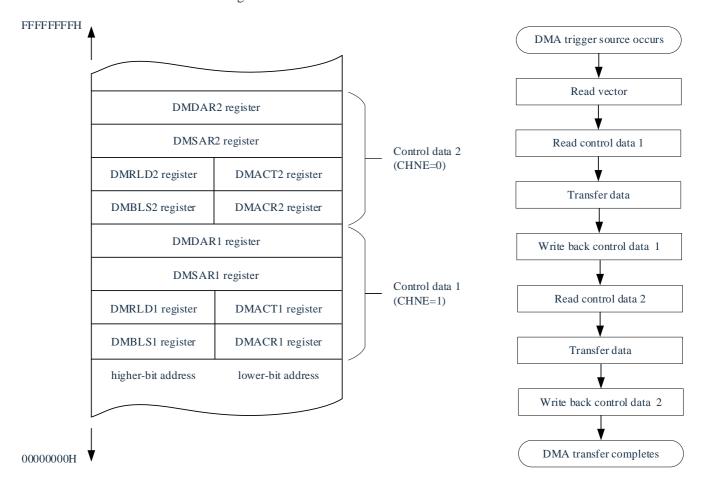

| 18.4.1     | Assignment of DMA Control Data Area and DMA Vector Table Area          | 376 |

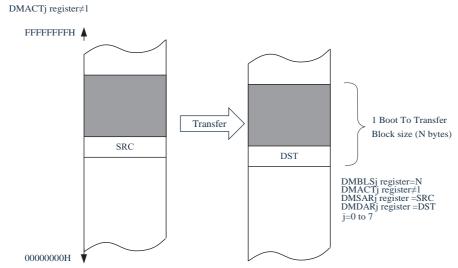

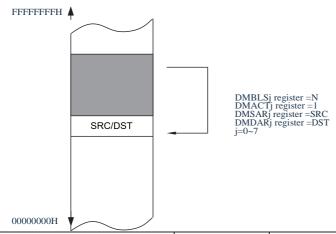

| 18.4.2     | Controlling Data Assignment                                            | 377 |

| 18.4.3     | Vector Table                                                           | 379 |

| 18.4.4     | Peripheral Enable Register 10 (PER10)                                  | 381 |

| 18.4.5     | DMA Trigger Source Selection Register (DMATGS)                         | 381 |

| 18.4.6     | Trigger Source Signal DMA Enable Register 0 (TGSEN0)                   | 382 |

| 18.4.7     | Trigger Source Signal DMA Enable Register 1 (TGSEN1)                   |     |

| 18.4.8     | Trigger Source Signal DMA Enable Register 2 (TGSEN2)                   |     |

| 18.4.9     | DMA Control Register j (DMACRj) (j=0~7)                                |     |

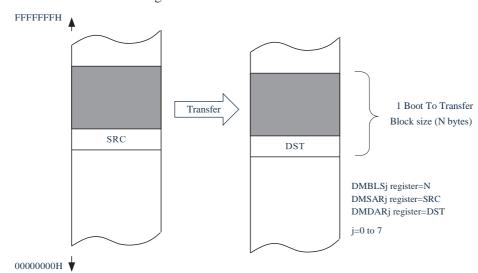

| 18.4.10    | DMA Block Size Register j (DMBLSj) (j=0~7)                             |     |

| 18.4.11    | DMA Transfer Count Register j (DMACTj) (j=0~7)                         |     |

| 18.4.12    | DMA Transfer Count Reload Register j (DMRLDj) (j=0~7)                  | 387 |

| 18.4.13    | DMA Source Address Register j (DMSARj) (j=0~7)                             | 388 |

|------------|----------------------------------------------------------------------------|-----|

| 18.4.14    | DMA Target Address Register j (DMDARj) (j=0~7)                             | 388 |

| 18.4.15    | DMA Start Enable Register i (DMAEN0)                                       | 389 |

| 18.4.16    | DMA Base Address Register (DMABAR)                                         | 390 |

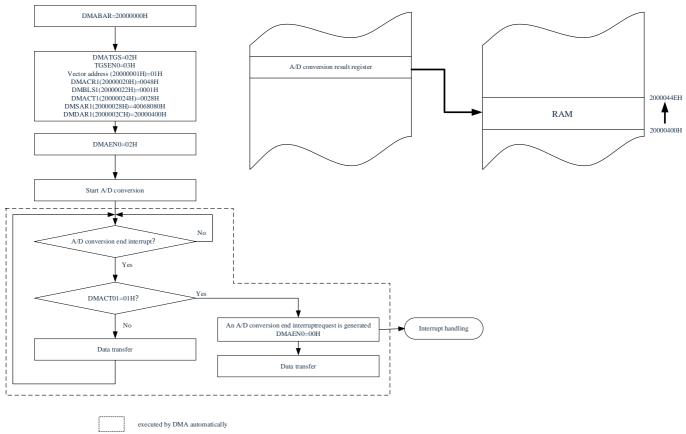

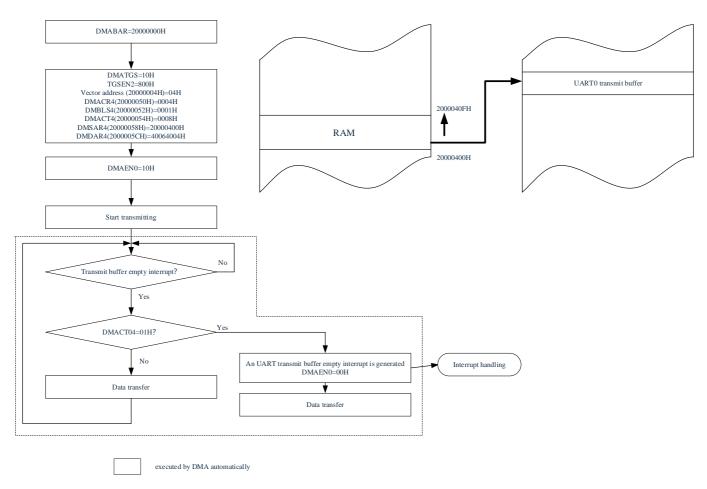

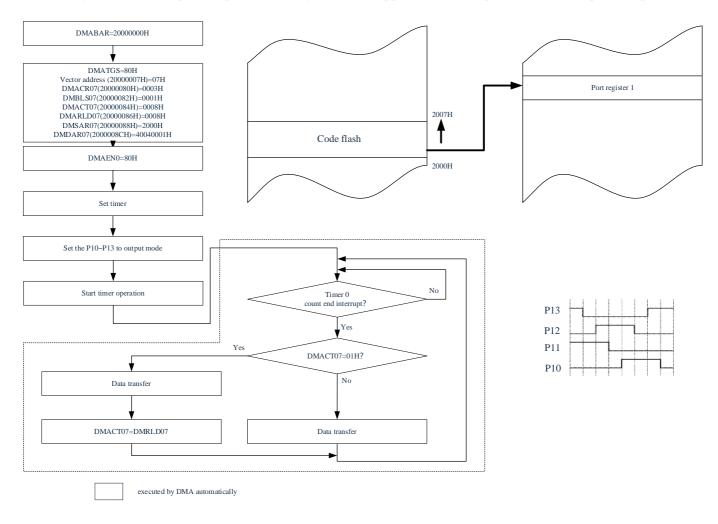

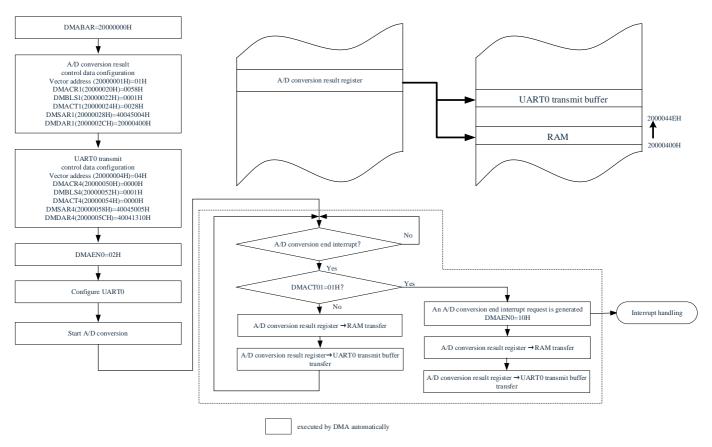

| 18.5 Ope   | ration of DMA                                                              | 391 |

| 18.5.1     | Start Sources                                                              | 391 |

| 18.5.2     | Normal Mode                                                                | 392 |

| 18.5.3     | Repeat Mode                                                                | 395 |

| 18.5.4     | Chain Transfer                                                             | 398 |

| 18.6 Cau   | tions When Using DMA                                                       | 400 |

| 18.6.1     | Settings of DMA Control Data and Vector Table                              | 400 |

| 18.6.2     | Assignment of DMA Control Data and Vector Table                            | 400 |

| 18.6.3     | Number of Execution Clocks for DMA                                         | 401 |

| 18.6.4     | Response Time for DMA                                                      | 402 |

| 18.6.5     | Start Source for DMA                                                       | 402 |

| 18.6.6     | Operation in Standby Mode                                                  | 402 |

| Chapter 19 | 9 A/D Converter (ADC)                                                      | 403 |

| -          |                                                                            |     |

|            | rview                                                                      |     |

|            | tures                                                                      |     |

|            | ction Description                                                          |     |

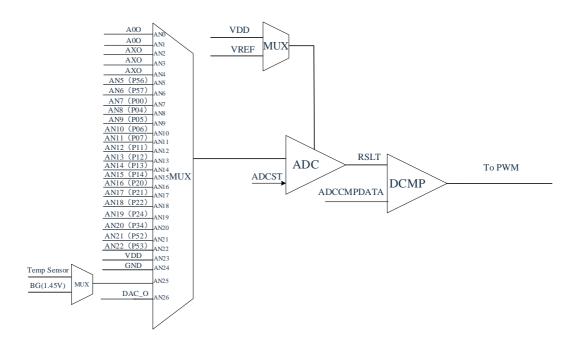

| 19.3.1     | ADC Channels                                                               |     |

| 19.3.2     | ADC Block Diagram                                                          |     |

| 19.3.3     | ADC Power Consumption Modes                                                |     |

| 19.3.4     | ADC Conversion Modes                                                       |     |

| 19.3.5     | ADC Clock                                                                  |     |

| 19.3.6     | ADC Channel Selection and Interrupt Generation.                            |     |

| 19.3.7     | ADC Software Start                                                         |     |

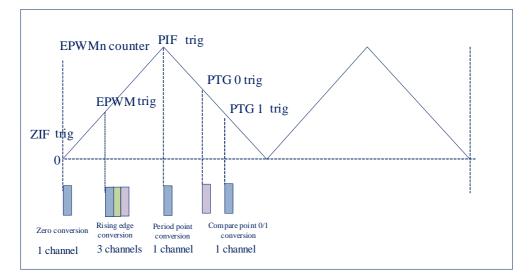

| 19.3.8     | ADC Hardware Trigger Start                                                 |     |

| C          | ister Mapping.                                                             |     |

| •          | ister Description                                                          |     |

| 19.5.1     | ADC Control Register (CON)                                                 |     |

| 19.5.2     | ADC Control Register 2 (CON2)                                              |     |

| 19.5.3     | ADC Hardware Trigger Control Register (HWTG)                               |     |

| 19.5.4     | ADC EPWM Trigger Delay Register (EPWMTGDLY)                                |     |

| 19.5.5     | ADC Scan Register (SCAN)                                                   |     |

| 19.5.6     | ADC EPWM Output Trigger Conversion Channel Enable Register (CHEPWM)        |     |

| 19.5.7     | ADC EPWM Period Point Trigger Conversion Channel Enable Register (CHPIFTG) |     |

| 19.5.8     | ADC EPWM Zero Point Trigger Conversion Channel Enable Bit (CHZIFTG)        |     |

| 19.5.9     | ADC EPWM Comparator 0 Trigger Conversion Channel Enable Register (CHPTG0)  |     |

| 19.5.10    | ADC EPWM Comparator 1 Trigger Conversion Channel Enable Register (CHPTG1)  |     |

| 19.5.11    | ADC Test Register (TEST)                                                   |     |

| 19.5.12    | ADC Conversion Result Register (RESULT)                                    |     |

| 19.5.13    | ADC Channel Conversion Result Register (DATAx) x=0~26                      |     |

| 19.5.14    | ADC Compare Control Register 0 (CMPx) x=0~1                                |     |

| 19.5.15    | ADC Interrupt Source Status Register (DIS)                                 |     |

| 19.5.16    | ADC Interrupt Source Status Register (RIS)                                 |     |

| 19.5.17    | ADC Enabled interrupt Status Register (MIS)                                | 422 |

|             | ADC Interrupt Clear Register (ICLR)                                                       |     |

|-------------|-------------------------------------------------------------------------------------------|-----|

| 19.5.19 A   | ADC Write Enable Control Register (LOCK)                                                  | 422 |

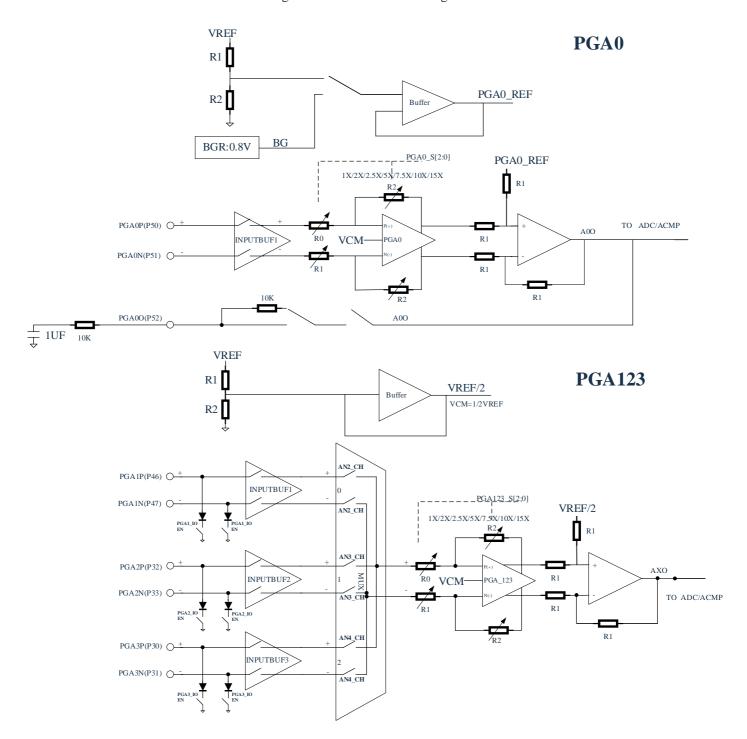

| Chapter 20  | Programmable Gain Amplifier (PGA0/1/2/3)                                                  | 423 |

| 20.1 Overv  | iew                                                                                       | 423 |

| 20.2 Featur | es                                                                                        | 423 |

| 20.3 Block  | Diagram of Structure                                                                      | 424 |

| 20.4 Regist | ter Mapping                                                                               |     |

| 20.5 Regist | ter Description                                                                           | 426 |

| 20.5.1 I    | PGA0 Control Register 0 (PGA0CON0)                                                        | 426 |

|             | PGA1/2/3 Control Register 0 (PGANCON0)                                                    |     |

|             | PGA1/2/3 Control Register 1 (PGANCON1)                                                    |     |

|             | PGA1/2/3 Input Channel Switch Register 1 (PGANSW)                                         |     |

| 20.5.5 I    | PGA Access Register Enable (PGALOCK)                                                      |     |

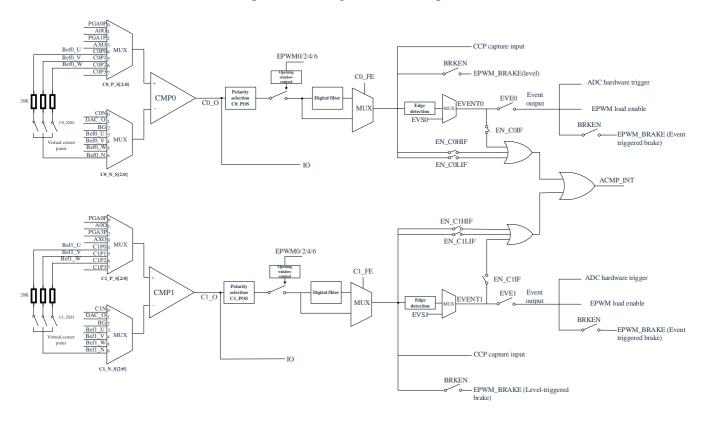

| Chapter 21  | Analog Comparator (ACMP0/1)                                                               | 429 |

| 21.1 Overv  | iew                                                                                       | 429 |

|             | Diagram of Structure                                                                      |     |

| 21.3 Featur | res                                                                                       | 430 |

| 21.4 Functi | ion Description                                                                           | 431 |

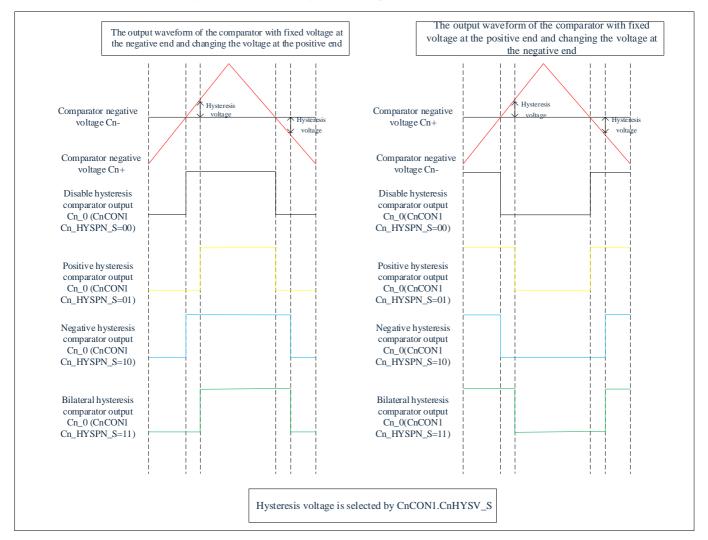

|             | Hysteresis Function                                                                       |     |

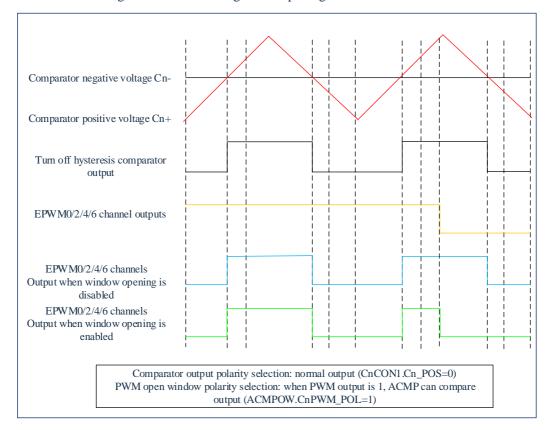

|             | Opening Window Control                                                                    |     |

|             | Filter Function                                                                           |     |

| _           | ter Mapping                                                                               |     |

| _           | ter Description                                                                           |     |

|             | Analog Comparator 0 Control Register 0 (C0CON0)                                           |     |

|             | Analog Comparator 0 Control Register 1 (C0CON1)                                           |     |

|             | Analog Comparator 1 Control Register 0 (C1CON0)                                           |     |

|             | Analog Comparator 1 Control Register 1 (C1CON1)                                           |     |

|             | Analog Comparator Event Control Register (CEVCON)                                         |     |

|             | Analog Comparator Interrupt Enable Register (IMSC)                                        |     |

|             | Analog Comparator Interrupt Source Status Register (RIS)                                  |     |

|             | Analog Comparator Enabled Interrupt Source Status Register (MIS)                          |     |

|             | Analog Comparator Interrupt Clear Control Register (ICLR)                                 |     |

|             | Analog Comparator Opening Window Control Register (ACMPOW)                                |     |

|             | Analog Comparator Write Enable Control Register (LOCK)  Digital-to-Analog Converter (DAC) |     |

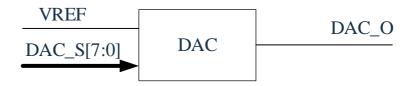

| Chapter 22  | iew                                                                                       |     |

|             |                                                                                           |     |

|             | Diagram of Structure                                                                      |     |

|             | res.                                                                                      |     |

| •           | ter Mapping                                                                               |     |

| •           | ter Description                                                                           |     |

|             | DAC Control Register 0 (CON0)                                                             |     |

|             | DAC Write Enable Control Register (LOCK)                                                  |     |

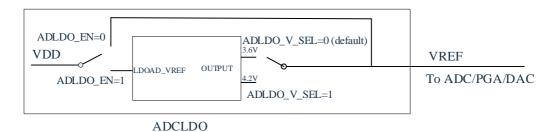

| Chapter 23  | ADCLDO                                                                                    |     |

|             | res.                                                                                      |     |

| 23.2 Block  | Diagram of Structure                                                                      | 446 |

| 447447447 |

|-----------|

| 447       |

|           |

| 119       |

| 440       |

| 448       |

| 449       |

| 450       |

| 451       |

| 452       |

| 452       |

| 452       |

| 452       |

| 453       |

| 453       |

| 454       |

| 454       |

| 455       |

| 455       |

| 456       |

| 456       |

| 457       |

|           |

|           |

| 459       |

| 459       |

| 460       |

| 460       |

| 462       |

| 463       |

| 463       |

| 465       |

| 466       |

| 468       |

|           |

| 469       |

| 471       |

| 475       |

| 475       |

| 475       |

| 477       |

| 477       |

| 478       |

| 479       |

| 482       |

|           |

| 28.1 Fur  | nctions of Voltage Detection Circuit                                 | 482 |

|-----------|----------------------------------------------------------------------|-----|

| 28.2 Str  | ucture of Voltage Detection Circuit                                  | 483 |

| 28.3 Reg  | gister Mapping                                                       | 483 |

| 28.4 Reg  | gisters for Controlling Voltage Detection Circuit                    | 483 |

| 28.4.1    | Voltage Detection Register (LVIM)                                    | 484 |

| 28.4.2    | Voltage Detection Level Register (LVIS)                              | 485 |

| 28.5 Ope  | eration of Voltage Detection Circuit                                 | 486 |

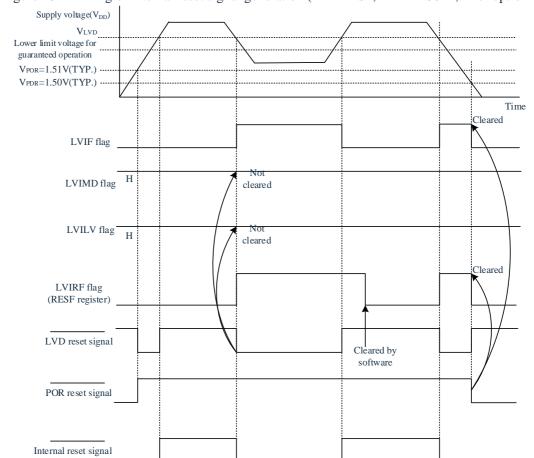

| 28.5.1    | When Used as Reset Mode                                              | 486 |

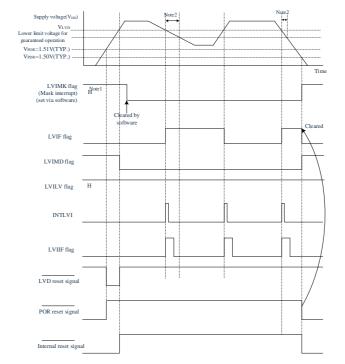

| 28.6 Wh   | nen Used As Interrupt Mode                                           | 487 |

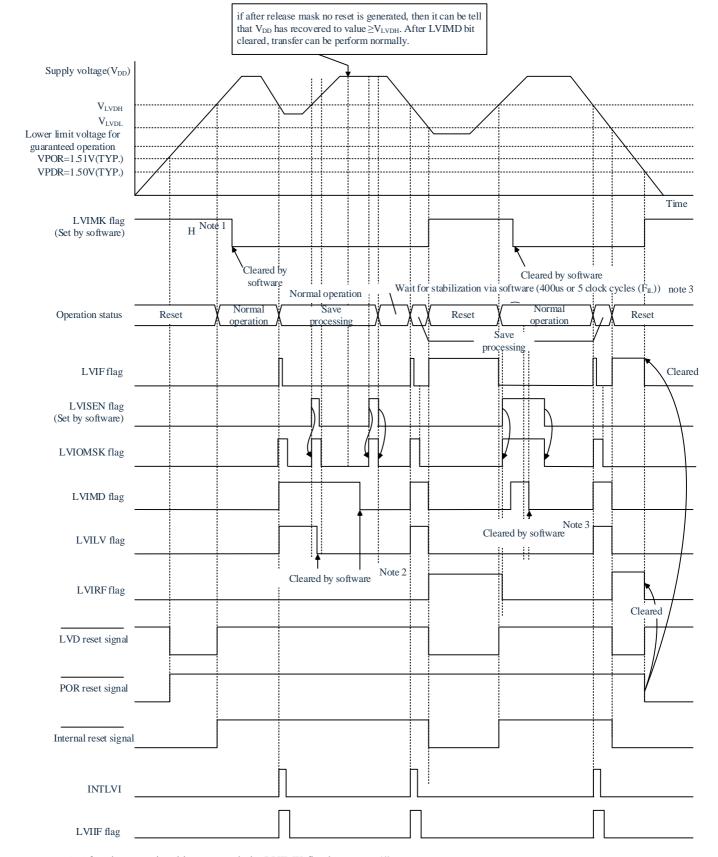

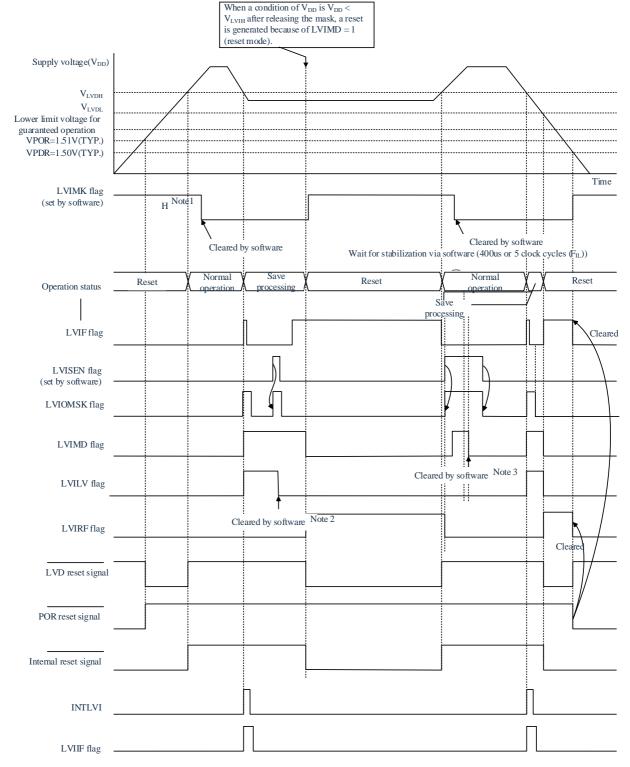

| 28.7 Wh   | nen Used as Interrupt & Reset Mode                                   | 488 |

| 28.8 Cau  | utions for Voltage Detection Circuit                                 | 494 |

| Chapter 2 | 9 Safety Functions                                                   | 496 |

| 29.1 Ove  | erview of Safety Functions                                           | 496 |

| 29.2 Reg  | gister Mapping                                                       | 497 |

| 29.3 Ope  | eration of Safety Functions                                          | 498 |

| 29.3.1    | Flash CRC Operation Function (High-Speed CRC)                        | 498 |

| 29.3.2    | SFR Guard Function                                                   |     |

| 29.3.3    | Frequency Detection Function                                         | 504 |

| 29.3.4    | A/D Test Function                                                    | 505 |

| 29.3.5    | Digital Output Signal Level Detection Function for Input/Output Pins | 506 |

| 29.3.6    | Product Unique ID Register                                           | 507 |

| Chapter 3 | Temperature Sensor                                                   | 508 |

| 30.1 Fur  | nctions of Temperature Sensors                                       | 508 |

| 30.2 Reg  | gister Mapping                                                       | 508 |

| 30.3 Ter  | nperature Sensor Register                                            | 508 |

| 30.3.1    | Temperature Sensor Calibration Data Register TSN25                   | 508 |

| 30.4 Inst | tructions for Using Temperature Sensors                              | 509 |

| Chapter 3 | Option Byte                                                          | 510 |

| 31.1 Fur  | nctions of Option Bytes                                              | 510 |

| 31.1.1    | User Option Bytes (000C0H~000C2H)                                    |     |

| 31.2 Fla  | sh Memory Data Protection Option Bytes (000C3H, 500004H)             |     |

|           | gister Mapping                                                       |     |

|           | er Option Bytes                                                      |     |

| 31.4.1    | User Option Byte 0 (000C0H)                                          |     |

| 31.4.2    | User Option Byte 1 (000C1H)                                          |     |

| 31.4.3    | User Option Byte 2 (000C2H)                                          |     |

| 31.4.4    | Flash Memory Data Protection Option Byte 1 (000C3H)                  | 518 |

| 31.4.5    | Flash Memory Data Protection Option Byte 2 (500004H)                 | 518 |

| Chapter 3 | 2 Flash Control                                                      | 519 |

| 32.1 Ove  | erivew of Flash Control                                              | 519 |

| 32.2 Str  | ucture of Flash Memory                                               | 519 |

| 32.3 Res  |                                                                      | 520 |

|           | gister Mapping                                                       | 520 |

| -         | gister Mappinggister Description                                     |     |

| -         |                                                                      | 520 |

| Chapter 34 | Appendix Revision History                           | 527 |

|------------|-----------------------------------------------------|-----|

| 33.2.2     | Test Register Access Enable Control Register        | 526 |

| 33.2.1     | Test Register 1(TEST1)                              | 526 |

| 33.2 Regis | ster Description                                    | 526 |

| 33.1 Regis | ster Mapping                                        | 526 |

| Chapter 33 | Test                                                | 526 |

| 32.6 Caut  | ions for Flash Operation                            | 525 |

| 32.5.3     | Word Program                                        |     |

| 32.5.2     | Chip Erase                                          |     |

| 32.5.1     | Sector Erase                                        |     |

| 32.5 How   | To Operate Flash                                    | 524 |

| 32.4.8     | Flash Write Time Control Register (FLPROCNT)        | 523 |

| 32.4.7     | Flash Sector Erase Time Control Register (FLSERCNT) | 522 |

| 32.4.6     | Flash Chip Erase Time Control Register (FLCERCNT)   | 522 |

| 32.4.5     | Flash Status Register (FLSTS)                       | 521 |

| 32.4.4     | Flash Erase Control Register (FLERMD)               | 521 |

| 32.4.3     | Flash Operation Control Register (FLOPMD2)          | 521 |

# Chapter 1 CPU

#### 1.1 Overview

This chapter provides a brief introduction to the features and debugging features of the ARM Cortex-M0+ core. For details, please refer to the ARM related documentation.

#### 1.2 Cortex-M0+ Core Features

- ARM Cortex-M0+ processor is a 32-bit RISC core with a 2-stage pipeline that supports privileged mode only.

- 1-cycle hardware multiplier

- Nested vector interrupt controller (NVIC)

- 1 non-maskable interrupt (NMI)

- Support 23 maskable interrupt requests (IRQ)

- 4 interrupt priority levels

- System Timer (SysTick) is a 24-bit countdown timer with a choice of F<sub>CLK</sub> or F<sub>IL</sub> count clock

- Vector table offset register (VTOR)

- The software can write VTOR to relocate the vector table start address to a different location.

- The default value of this register is 0x0000\_0000, the lower 8 bits are ignored for writing and zero for reading, which means the offset is 256 bytes aligned.

### 1.3 Debugging Features

- 2-wire SWD debug interface

- Support for pausing, resuming and single-step execution of programs

- Access to the processor's core registers and special function registers

- 4 hardware breakpoints (BPU)

- Unlimited software breakpoints (BKPT instruction)

- 2 data observation points (DWT)

- Accessing memory while the core is executing

www.mcu.com.cn 16 / 527 Rev.1.0.1

MCU Debug Support

Cortex-MO+ Debug Support

Cortex-MO+ Core

Bus Matrix

Bridge

NVIC

Debug AP

Debug AP

DBGM

CU

BPU

Figure 1-1 Debug block diagram of Cortex-M0+

Note: SWD does not work in deep sleep mode, please do debug operation in active and sleep mode.

www.mcu.com.cn 17 / 527 Rev.1.0.1

### 1.4 SWD Interface Pins

The 2 GPIOs of this product can be used as SWD interface pins, which exist in all packages.

Table 1-1 SWD debug port pins

| SWD port name | Debugging function       | Pin assignment |

|---------------|--------------------------|----------------|

| SWCLK         | Serial clock             | P03            |

| SWDIO         | Serial data input/output | P02            |

When the SWD function is not used, the SWD can be disabled by setting the debug stop control register (DBGSTOPCR).

| Bit   | Symbol | Description                                                                                                                                                                                                                                       | Reset value |

|-------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 31:25 | -      | Reserved                                                                                                                                                                                                                                          | -           |

| 24    | SWDIS  | SWD debug interface status  0: Enable the SWD debug interface. P02/P03 cannot be used as GPIO (because ENO and DOUT of this IOBUF are controlled by the debugger at this time).  1: Disable the SWD debug interface. P02/P03 can be used as GPIO. | 0           |

| 23:2  | -      | Reserved                                                                                                                                                                                                                                          | 0x0         |

| 1     | FRZEN1 | When the debugger is connected and the CPU is in debug state (HALTED=1), the peripheral module of the communication system acts/stops Note 2  0: Peripheral acts 1: Peripheral stops                                                              | 0           |

| 0     | FRZEN0 | When the debugger is connected and the CPU is in debug state (HALTED=1), the timer system peripheral module acts/stops Note 1  0: Peripheral acts 1: Peripheral stops                                                                             | 0           |

Note 1: The timer system peripheral module of this product includes: general-purpose timer unit (Timer4).

Note 2: The communication system peripheral module of this product includes: serial communication unit, serial IICA.

www.mcu.com.cn 18 / 527 Rev.1.0.1

### 1.5 ARM Reference Documents

The built-in debugging feature in the  $Cortex^{@}$ -M0+ core is part of the ARM $^{@}$  CoreSight design suite. For documentation, refer to:

- Cortex®-M0+ Technical Reference Manual (TRM)

- ARM® Debug Interface V5

- ARM® CoreSight Design Suite Version r1p1 Technical Reference Manual

www.mcu.com.cn 19 / 527 Rev.1.0.1

# **Chapter 2 Pin Functions (GPIO)**

### 2.1 Port Functions

For detailed information, please refer to the datasheet of the corresponding product series.

#### 2.2 Port Alternate Function

For detailed configuration of each alternate function, please refer to the datasheet of the corresponding product series. See the table below for details of the port alternate function.

Table 2-1 Port alternate function digital mapping table

| D. C          | T                     |   | Alternat | te function (PmnCFG) |          |

|---------------|-----------------------|---|----------|----------------------|----------|

| Function name | Input                 | 0 | 1        | 2                    | 3        |

| P00           | HALL_IN0/RXD0/CCP0A_I |   | TXD0     | CCP0A_O              | ADC_TRIG |

| P01           | NRST/RXD0/CCP0B_I     |   | TXD0     | CCP0B_O              | ADC_TRIG |

| P02           | CCP1A_I               |   | -        | CCP1A_O              | -        |

| P03           | CCP1B_I               |   | -        | CCP1B_O              | ADC_TRIG |

| P04           | CCP1A_I               |   | C0_O     | CCP1A_O              | SCL      |

| P05           | CCP1B_I               |   | -        | CCP1B_O              | SDA      |

| P06           | CCP0A_I               |   | NSS      | CCP0A_O              | SCL      |

| P07           | CCP0B_I               |   | SCLK     | CCP0B_O              | SDA      |

| P10           | ADET                  |   | MOSI     | -                    | -        |

| P11           | CCP1A_I               |   | MISO     | CCP1A_O              | C0_O     |

| P12           | CCP1B_I               |   | -        | CCP1B_O              | -        |

| P13           | BKIN                  |   | -        | -                    | -        |

| P14           | -                     |   | MISO     | PCUBZ0               | SCL      |

| P15           | RXD0                  |   | MOSI     | TXD0                 | SDA      |

| P16           | BKIN/RXD0             |   | SCLK     | TXD0                 | -        |

| P17           | -                     |   | NSS      | -                    | ADC_TRIG |

| P20           | HALL_IN0              |   | -        | -                    | -        |

| P21           | HALL_IN1              |   | -        | -                    | ADC_TRIG |

| P22           | HALL_IN2              |   | -        | -                    | ADC_TRIG |

| P23           | BKIN/RXD1/CCP0B_I     |   | TXD1     | CCP0B_O              | C1_O     |

| P24           | RXD1/CCP0A_I          |   | TXD1     | CCP0A_O              | ADC_TRIG |

| P25           | RXD1/CCP1A_I          |   | TXD1     | CCP1A_O              | C1_O     |

| P30           | -                     |   | -        | -                    | -        |

| P31           | -                     | - | -        | -                    | -        |

| P32           | -                     |   | -        | -                    | -        |

| P33           | -                     |   | -        | -                    | -        |

| P34           | RXD0                  |   | TXD0     | -                    | SDA      |

| P35           | RXD0                  |   | TXD0     | -                    | SCL      |

| P36           | -                     |   | EPWM0    | -                    | -        |

| P37           | -                     |   | EPWM1    | -                    | -        |

| P40           | -                     |   | EPWM2    | -                    | -        |

| P41           | -                     |   | EPWM3    | -                    | -        |

| P42           | -                     |   | EPWM4    | -                    | -        |

www.mcu.com.cn 20 / 527 Rev.1.0.1

#### CMS32M67xx User Manual | Chapter 2 Pin Functions (GPIO)

| P43 | -                 | EPWM5 | -       | -   |

|-----|-------------------|-------|---------|-----|

| P44 | -                 | EPWM6 | -       | -   |

| P45 | -                 | EPWM7 | -       | -   |

| P46 | -                 | -     | -       | -   |

| P47 | -                 | -     | -       | -   |

| P50 | -                 | -     | -       | -   |

| P51 | -                 | -     | -       | -   |

| P52 | CCP0B_I           | -     | CCP0B_O | -   |

| P53 | RXD1/ CCP1B_I     | TXD1  | CCP1B_O | -   |

| P54 | RXD1              | TXD1  | -       | SCL |

| P55 | BKIN/RXD1         | TXD1  | -       | SDA |

| P56 | HALL_IN2/CCP1A_I  | -     | CCP1A_O |     |

| P57 | HALL_IN1/ CCP1B_I | -     | CCP1B_O |     |

Note 1: This product requires users to configure PMC, PM, and other registers separately for the IO alternate function.

Note 2: When selecting the IIC function, the open-drain function is automatically enabled.

Note 3: Regarding the multiplexing function, it can be used for both input and output. Once the PmnCFG is selected, the input channel is automatically enabled.

www.mcu.com.cn 21 / 527 Rev.1.0.1

Table 2-2 Analog function and special function pins

| Pin  |      | Analog |          | Special function pin |

|------|------|--------|----------|----------------------|

| TIII | ADC  | ACMP   | PGA      | Special function pin |

| P00  | AN7  | C0P0   | -        | -                    |

| P01  | -    | -      | -        | NRST                 |

| P02  | -    | -      | -        | SWDDAT               |

| P03  | -    | -      | -        | SWDCLK               |

| P04  | AN8  | -      | -        | OSCOUT               |

| P05  | AN9  | -      | -        | OSCIN                |

| P06  | AN10 | -      | -        | -                    |

| P07  | AN11 | -      | -        | -                    |

| P10  | -    | -      |          | -                    |

| P11  | AN12 | -      | -        | -                    |

| P12  | AN13 | -      | -        | DAC_O                |

| P13  | AN14 | -      | -        | -                    |

| P14  | AN15 | -      | -        | -                    |

| P15  | -    | -      | -        | -                    |

| P16  | -    | -      | -        | -                    |

| P17  | -    | -      | -        | -                    |

| P20  | AN16 | C1P0   | -        | -                    |

| P21  | AN17 | C1P1   | -        | -                    |

| P22  | AN18 | C1P2   | -        | -                    |

| P23  | -    | C1P3   | -        | -                    |

| P24  | AN19 | CIN    | -        | -                    |

| P25  | -    | -      | -        | -                    |

| P30  | -    | -      | PGA3_P   | -                    |

| P31  | -    | -      | PGA3_N   | -                    |

| P32  | -    | -      | PGA2_P   | -                    |

| P33  | -    | -      | PGA2_N   | -                    |

| P34  | AN20 | -      | -        | -                    |

| P35  | -    | -      | -        | -                    |

| P36  | -    | -      | -        | -                    |

| P37  | -    | -      | -        | -                    |

| P40  | -    | -      | -        | -                    |

| P41  | -    | -      | -        | -                    |

| P42  | -    | -      | -        | -                    |

| P43  | -    | -      | -        | -                    |

| P44  |      | -      | -        | -                    |

| P45  | -    | -      | -        | -                    |

| P46  | -    | -      | PGA1_P   | -                    |

| P47  | -    | -      | PGA1_N   | -                    |

| P50  | -    | -      | PGA0_P   | -                    |

| P51  | -    | -      | PGA0_N   | -                    |

| P52  | AN21 | -      | PGA0_O   | -                    |

| P53  | AN22 | -      | PGA123_O | DAC_O                |

| P54  | -    | C0P3   | -        | -                    |

| P55  | -    | C0N    | -        | -                    |

| P56  | AN5  | C0P2   | -        | -                    |

| P57  | AN6  | C0P1   | -        | -                    |

# 2.3 Register Mapping

# 2.3.1 Control Function Register Mapping

(Base address of the port control register =0x40040000) RO: Read only, WO: Write only, R/W: Read/Write

| Register | Offset value | R/W | Description                                                 | Reset value |

|----------|--------------|-----|-------------------------------------------------------------|-------------|

| P0       | 0x000        | R/W |                                                             | 0x00        |

| P1       | 0x001        | R/W | Set the register for configuring the output latch value in  | 0x00        |

| P2       | 0x002        | R/W | 1-bit units; read this register in input mode to get the    | 0x00        |

| Р3       | 0x003        | R/W | pin level, and in output mode to get the value of the       | 0x00        |

| P4       | 0x004        | R/W | port's output latch.                                        | 0x00        |

| P5       | 0x005        | R/W |                                                             | 0x00        |

| PM0      | 0x020        | R/W |                                                             | 0xFF        |

| PM1      | 0x021        | R/W |                                                             | 0xFF        |

| PM2      | 0x022        | R/W | When the port is used as a digital channel, the registers   | 0xFF        |

| PM3      | 0x023        | R/W | for the input or output of the port are set in 1-bit units. | 0xFF        |

| PM4      | 0x024        | R/W |                                                             | 0xFF        |

| PM5      | 0x025        | R/W |                                                             | 0xFF        |

| PU0      | 0x030        | R/W |                                                             | 0x0E        |

| PU1      | 0x031        | R/W | The internal pull-up resistor selection register of the     | 0x00        |

| PU2      | 0x032        | R/W | port can only be set when the corresponding                 | 0x00        |

| PU3      | 0x033        | R/W | PMCmn=0, the pull-up resistor is valid. The pull-up         | 0x00        |

| PU4      | 0x034        | R/W | function of P01, P02 and P03 is enabled by default.         | 0x00        |

| PU5      | 0x035        | R/W | Tunction of 1 o1, 1 o2 and 1 o3 is chapted by default.      | 0x00        |

| PD0      | 0x040        | R/W |                                                             | 0x00        |

| PD1      | 0x041        | R/W | The internal pull-down resistor selection register of the   | 0x00        |

| PD2      | 0x042        | R/W | port can only be set when the corresponding                 | 0x00        |

| PD3      | 0x043        | R/W | PMCmn=0, the pull-down resistor is valid. P01 has no        | 0x00        |

| PD4      | 0x044        | R/W | pull-down function.                                         | 0x00        |

| PD5      | 0x045        | R/W | pun-down function.                                          | 0x00        |

| POM0     | 0x050        | R/W |                                                             | 0x00        |

| POM1     | 0x051        | R/W |                                                             | 0x00        |

| POM2     | 0x052        | R/W | Open Drain Mode Register, N-Channel Open Drain              | 0x00        |

| POM3     | 0x053        | R/W | will be turned on only when the port is configured for      | 0x00        |

| POM4     | 0x054        | R/W | Output Mode.                                                | 0x00        |

| POM5     | 0x055        | R/W |                                                             | 0x00        |

| PMC0     | 0x060        | R/W |                                                             | 0xC1        |

| PMC1     | 0x061        | R/W |                                                             | 0xFF        |

| PMC2     | 0x062        | R/W | Port Mode Register, sets the port to be used as a digital   | 0xFF        |

| PMC3     | 0x063        | R/W | or analog channel in 1-bit units; P00, P01, P02, P03,       | 0xFF        |

| PMC4     | 0x064        | R/W | P04, and P05 are used as digital channels by default.       | 0xFF        |

| PMC5     | 0x065        | R/W | 7                                                           | 0xFF        |

| PSET0    | 0x070        | W   |                                                             | 0x00        |

| PSET1    | 0x071        | W   | 7                                                           | 0x00        |

| PSET2    | 0x072        | W   | ]                                                           | 0x00        |

| PSET3    | 0x073        | W   | Sets the registers of the port output latch in 1-bit units. | 0x00        |

| PSET4    | 0x074        | W   | <b> </b>                                                    | 0x00        |

| PSET5    | 0x075        | W   | ╡                                                           | 0x00        |

### CMS32M67xx User Manual | Chapter 2 Pin Functions (GPIO)

| PCLR0 | 0x080 | W |                                                       | 0x00 |

|-------|-------|---|-------------------------------------------------------|------|

| PCLR1 | 0x081 | W |                                                       | 0x00 |

| PCLR2 | 0x082 | W |                                                       | 0x00 |

| PCLR3 | 0x083 | W | Clear the port output latch registers in 1-bit units. | 0x00 |

| PCLR4 | 0x084 | W |                                                       | 0x00 |

| PCLR5 | 0x085 | W |                                                       | 0x00 |

www.mcu.com.cn 24 / 527 Rev.1.0.1

# 2.3.2 Output-Input Alternate Function Register Mapping

(Base address of the output-input alternate function register=0x40040800)

RO: Read only, WO: Write only, R/W: Read/Write

| Register | Offset value | R/W        | Description                                                                                              | Reset value |

|----------|--------------|------------|----------------------------------------------------------------------------------------------------------|-------------|

| POOCFG   | 0x00         | R/W<br>R/W | Description                                                                                              | 0x00        |

| P01CFG   | 0x02         | R/W        | -                                                                                                        | 0x00        |

|          | 0x04         | R/W        | -                                                                                                        | 0x00        |

| P02CFG   | 0x06         | R/W        | -                                                                                                        | 0x00        |

| P03CFG   | 0x08         | R/W        |                                                                                                          | 0x00        |

| P04CFG   |              |            |                                                                                                          |             |

| P05CFG   | 0x0A         | R/W        | -                                                                                                        | 0x00        |

| P06CFG   | 0x0C         | R/W        | -                                                                                                        | 0x00        |

| P07CFG   | 0x0E         | R/W        | -                                                                                                        | 0x00        |

| P10CFG   | 0x10         | R/W        | -                                                                                                        | 0x00        |

| P11CFG   | 0x12         | R/W        | _                                                                                                        | 0x00        |

| P12CFG   | 0x14         | R/W        | _                                                                                                        | 0x00        |

| P13CFG   | 0x16         | R/W        |                                                                                                          | 0x00        |

| P14CFG   | 0x18         | R/W        |                                                                                                          | 0x00        |

| P15CFG   | 0x1A         | R/W        |                                                                                                          | 0x00        |

| P16CFG   | 0x1C         | R/W        |                                                                                                          | 0x00        |

| P17CFG   | 0x1E         | R/W        |                                                                                                          | 0x00        |

| P20CFG   | 0x20         | R/W        |                                                                                                          | 0x00        |

| P21CFG   | 0x22         | R/W        |                                                                                                          | 0x00        |

| P22CFG   | 0x24         | R/W        |                                                                                                          | 0x00        |

| P23CFG   | 0x26         | R/W        | Port output alternate configuration register allows                                                      | 0x00        |

| P24CFG   | 0x28         | R/W        | mapping the output functionality of peripheral modules to the corresponding ports. For specific pin      | 0x00        |

| P25CFG   | 0x2A         | R/W        | function digit mapping, please refer to Table 2-1.                                                       | 0x00        |

| P30CFG   | 0x30         | R/W        | The reset value of the port output alternate function                                                    | 0x00        |

| P31CFG   | 0x32         | R/W        | register is 0x00, which corresponds to the default—<br>alternate function and GPIO function of the port. | 0x00        |

| P32CFG   | 0x34         | R/W        | 7                                                                                                        | 0x00        |

| P33CFG   | 0x36         | R/W        | 7                                                                                                        | 0x00        |

| P34CFG   | 0x38         | R/W        | 7                                                                                                        | 0x00        |

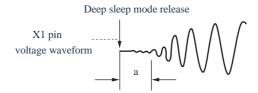

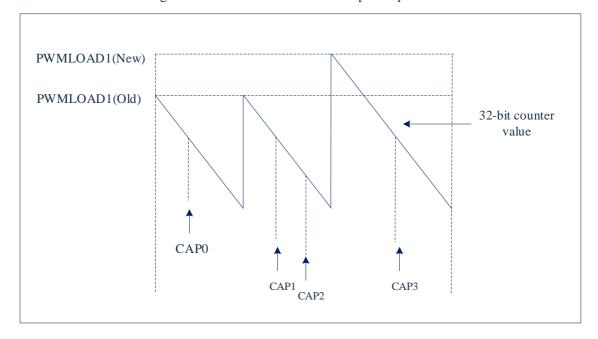

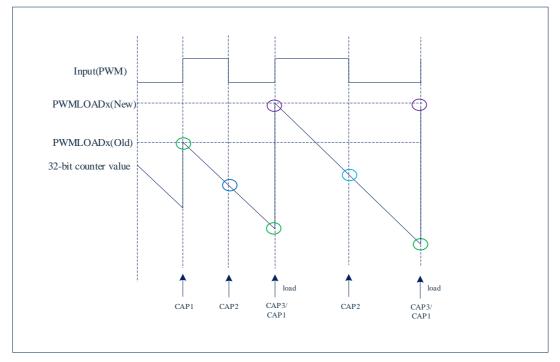

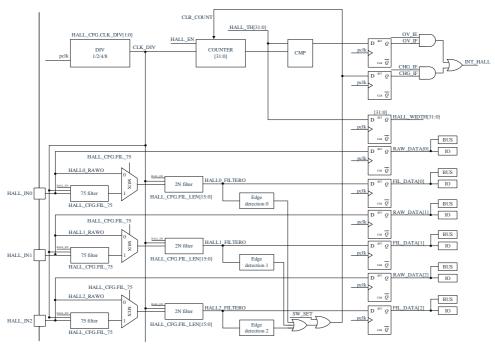

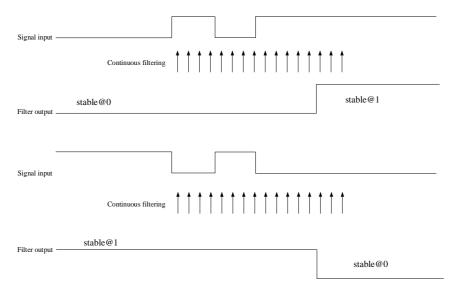

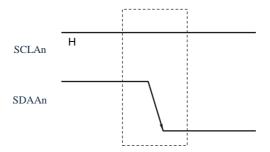

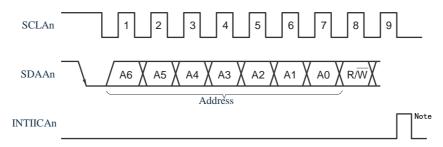

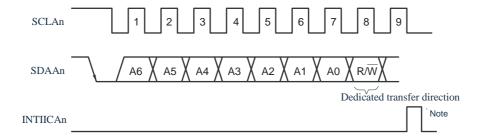

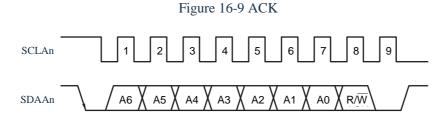

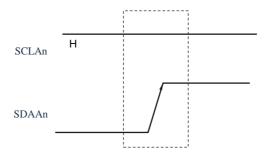

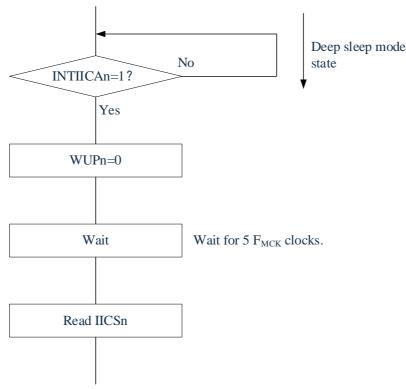

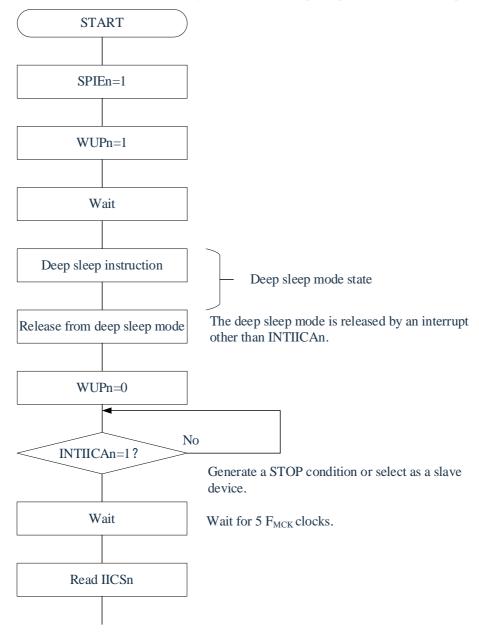

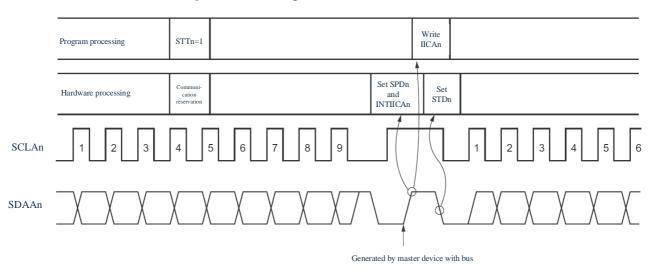

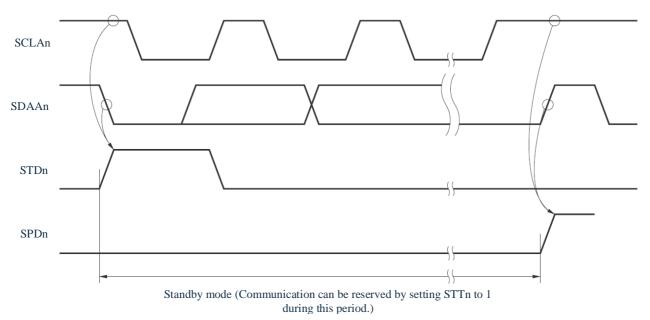

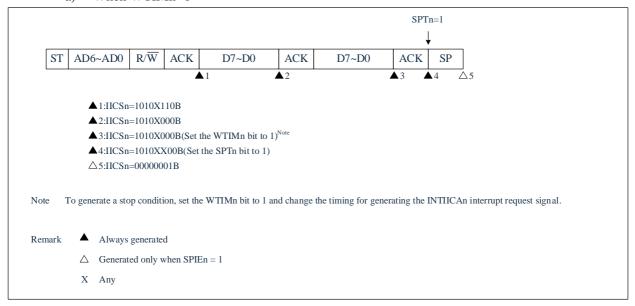

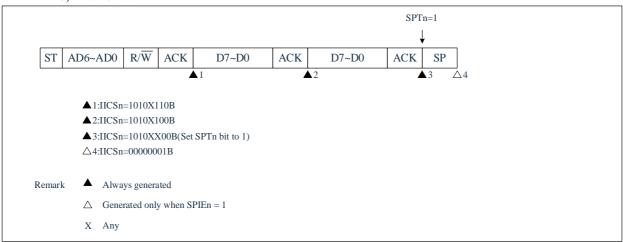

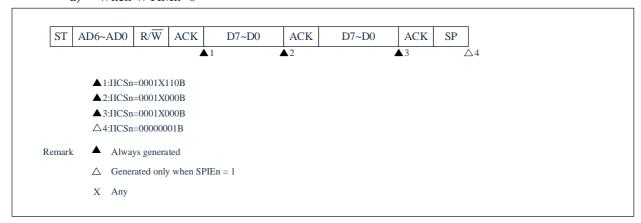

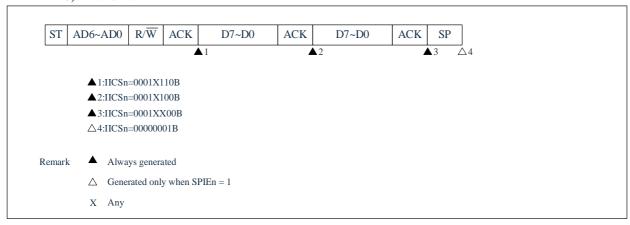

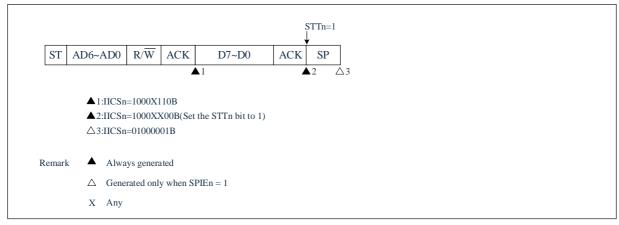

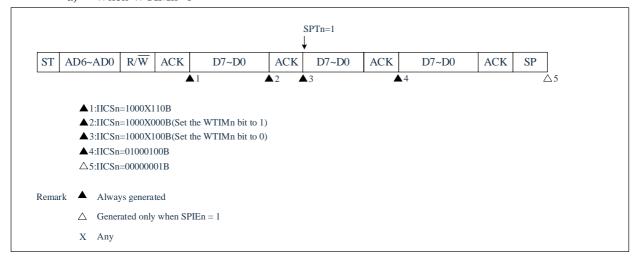

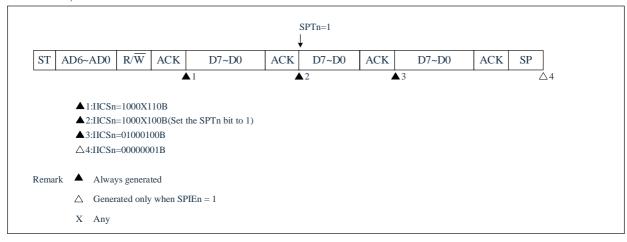

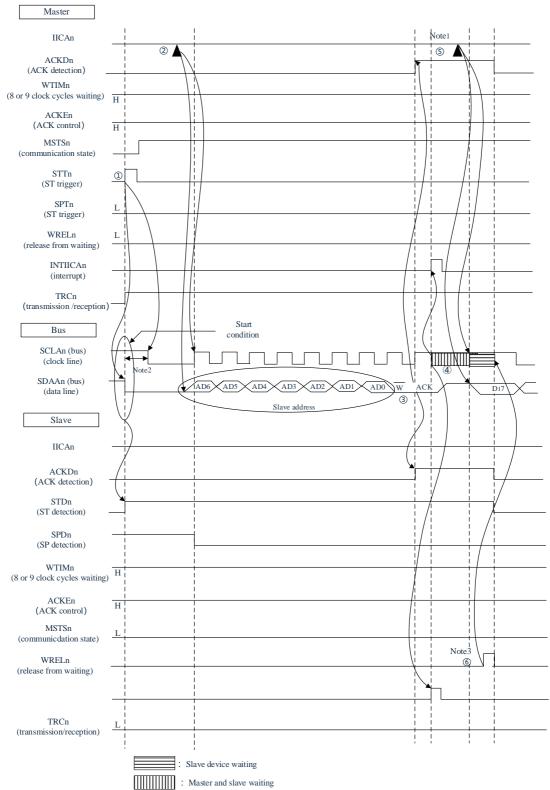

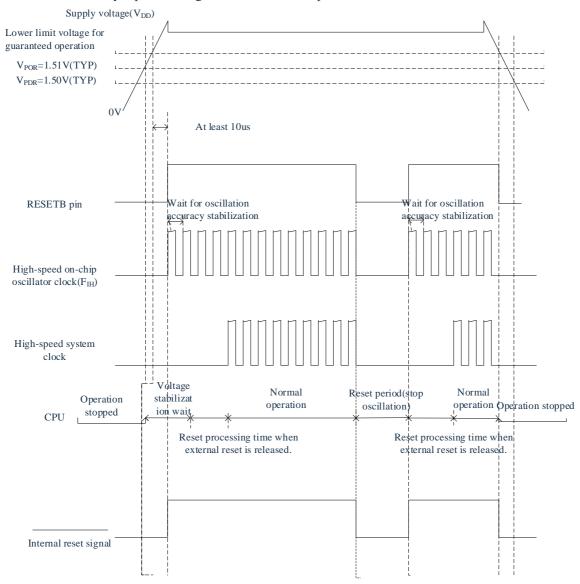

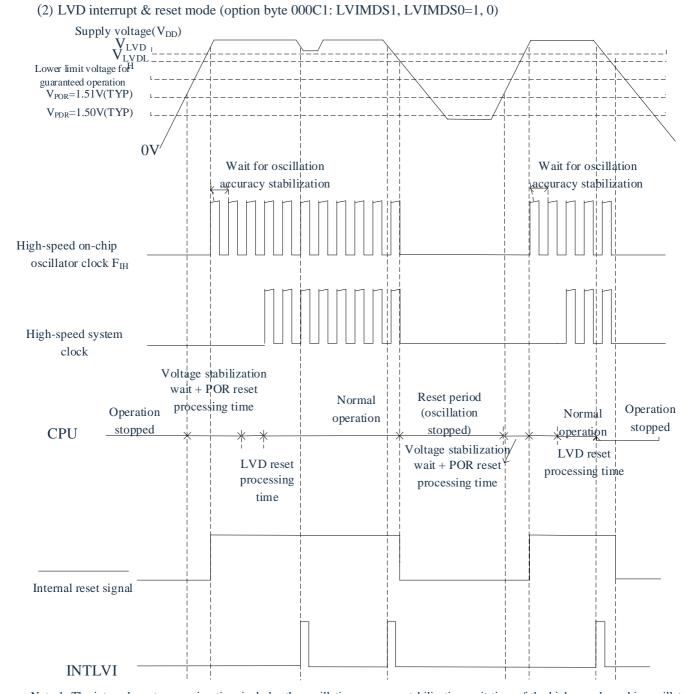

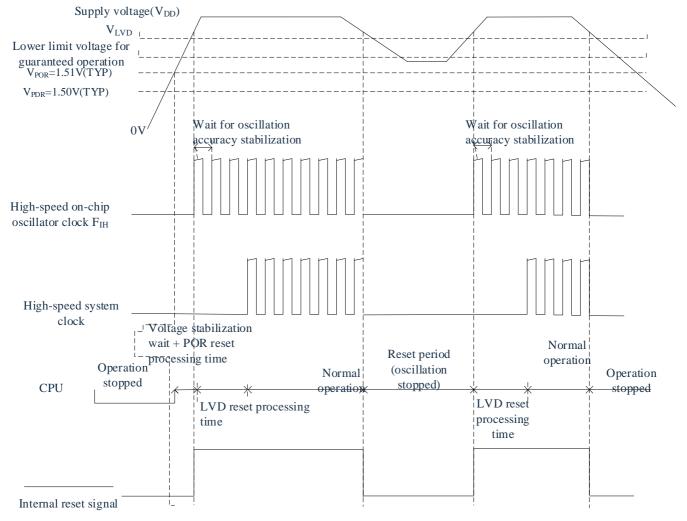

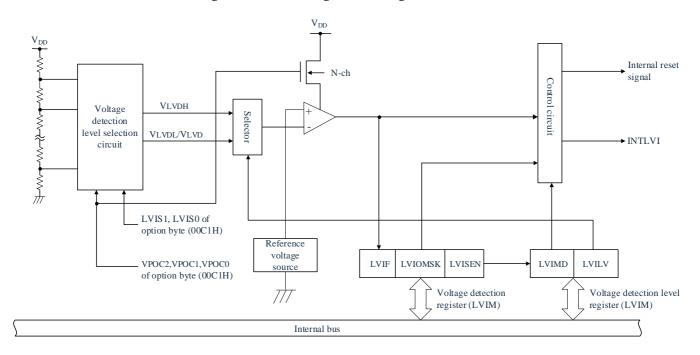

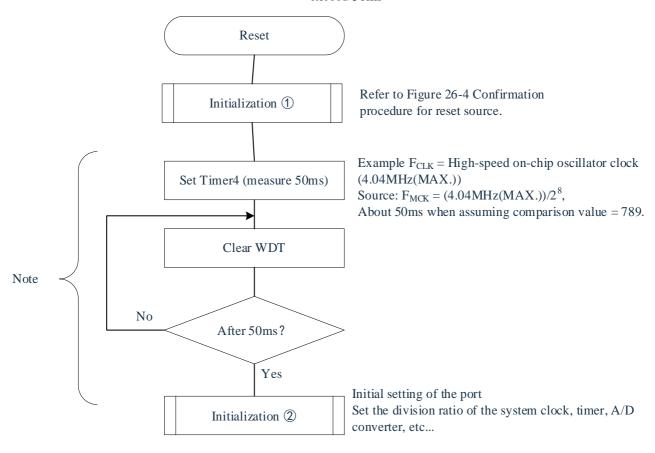

| P35CFG   | 0x3A         | R/W        | 7                                                                                                        | 0x00        |